Other Parts Discussed in Thread: DLP160CP, DLPA2005, DLPC3436

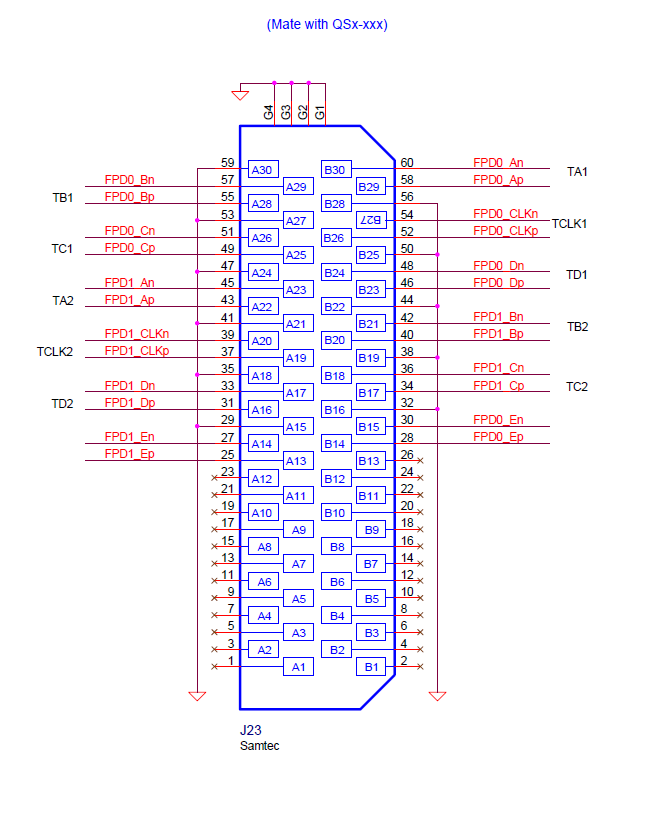

问题1:DLPC3421的数据手册里表明适用于DLP160CP DMD的显示控制,并且支持HD 模式配置(1280 × 720 像素屏幕显示),在HD模式前端需要搭配FPGA(XC7S50-2CSGA324C4493),我们现在正在做HD模式的设计,使用

0.16DMD+振镜+DLPC3421+DLPA2005实现720P的显示,但在官网资料中未找到关于XC7S50-2CSGA324C4493的相关设计。我从哪里可以获取到

1、XC7S50-2CSGA324C4493 + DLCP3421 的原理图参考设计;

2、XC7S50-2CSGA324C4493的固件(.bit或者.bin),实现1280 × 720输入,4个640x360的子帧输出以及振镜控制的同步;

3、XC7S50-2CSGA324C4493的输入接口能否是Parallel,而不是FPD-Link;

问题2:DLPC3436前端的FPGA是XC7Z020-1CLG484I,这个FPGA是否能适用于DLPC3421来实现HD模式呢?我们希望最终能实现同一块FPGA能兼容DLPC3436和DLPC3421两种设计;