Part Number: DS90UB983-Q1

Other Parts Discussed in Thread: DS90UB984-Q1

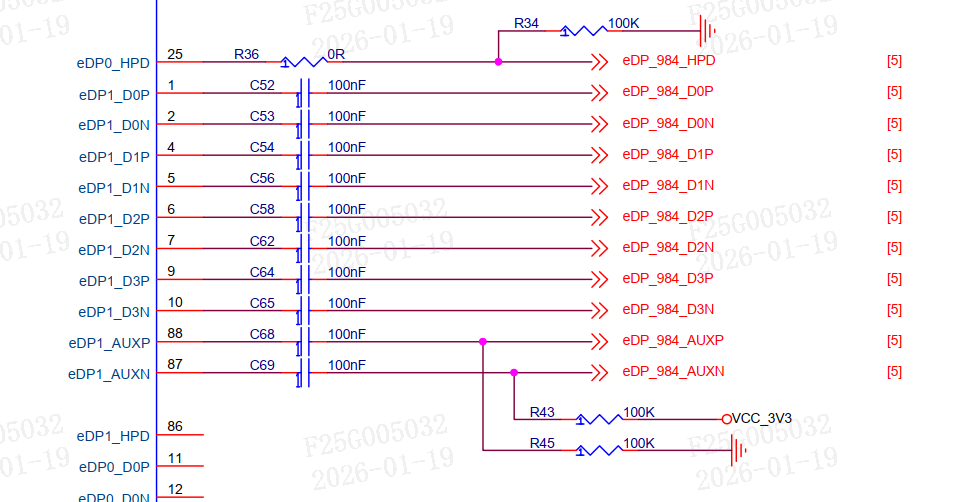

加串器使用UB983,解串器使用UB984,使用DP1进行输出,但发现硬件设计错误,现在把eDP1_HPD的86引脚飞线到R36,但984打pattern仍不出图

Part Number: DS90UB983-Q1

Other Parts Discussed in Thread: DS90UB984-Q1

加串器使用UB983,解串器使用UB984,使用DP1进行输出,但发现硬件设计错误,现在把eDP1_HPD的86引脚飞线到R36,但984打pattern仍不出图

这里有几个问题:

系统层面问题:

一级供应商/原始设备制造商?

新的设计还是生产系统?

串行器/解串器部件编号?

FPD-Link III 或 IV 模式?

分辨率、色彩深度、PCLK 频率?

FPD-Link 模式/FPD 速率?

DPRX/DPTX 速率?

系统芯片/源设备?

已构建的系统数量与故障设备数量之比?

单个或多个显示器/主机/电子控制单元/车辆控制单元系统?

故障模式详情:

观察到的问题(黑屏/闪烁/无锁定/失真/间歇性出现)?

问题发生的时间:启动时/运行时等?

重现频率?

环境:车辆/测试台?

恢复方法:自动/软重启/硬重启/电源重启/重新初始化?

温度依赖性:室温/低温/高温?

关于故障模式:

你能说明一下你的设置情况吗?也就是说,983 与 984 相连,但你却试图将数据输出到本地的“patgen”设备上?

问题在于,您看到的是 984 个链接训练失败的情况?

您是否已正确将视频流映射到 DP1 了?

您在此处设置的是什么 DPTX 速率和通道数量?

能否发送您的脚本以便审核?

请使用以下脚本来记录故障模式发生时的情况。

## TI Confidential - NDA Restrictions

##

## Copyright 2018 Texas Instruments Incorporated. All rights reserved.

##

## IMPORTANT: Your use of this Software is limited to those specific rights

## granted under the terms of a software license agreement between the user who

## downloaded the software, his/her employer (which must be your employer) and

## Texas Instruments Incorporated (the License). You may not use this Software

## unless you agree to abide by the terms of the License. The License limits your

## use, and you acknowledge, that the Software may not be modified, copied or

## distributed unless embedded on a Texas Instruments microcontroller which is

## integrated into your product. Other than for the foregoing purpose, you may

## not use, reproduce, copy, prepare derivative works of, modify, distribute,

## perform, display or sell this Software and/or its documentation for any

## purpose.

##

## YOU FURTHER ACKNOWLEDGE AND AGREE THAT THE SOFTWARE AND DOCUMENTATION ARE

## PROVIDED AS IS WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED,

## INCLUDING WITHOUT LIMITATION, ANY WARRANTY OF MERCHANTABILITY, TITLE,

## NON-INFRINGEMENT AND FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL TEXAS

## INSTRUMENTS OR ITS LICENSORS BE LIABLE OR OBLIGATED UNDER CONTRACT,

## NEGLIGENCE, STRICT LIABILITY, CONTRIBUTION, BREACH OF WARRANTY, OR OTHER LEGAL

## EQUITABLE THEORY ANY DIRECT OR INDIRECT DAMAGES OR EXPENSES INCLUDING BUT NOT

## LIMITED TO ANY INCIDENTAL, SPECIAL, INDIRECT, PUNITIVE OR CONSEQUENTIAL

## DAMAGES, LOST PROFITS OR LOST DATA, COST OF PROCUREMENT OF SUBSTITUTE GOODS,

## TECHNOLOGY, SERVICES, OR ANY CLAIMS BY THIRD PARTIES (INCLUDING BUT NOT

## LIMITED TO ANY DEFENSE THEREOF), OR OTHER SIMILAR COSTS.

##

## Should you have any questions regarding your right to use this Software,

## contact Texas Instruments Incorporated at www.TI.com.

## Debug Script Version 1

import time

#######################User_Input############################

serAddr = 0x18

desAlias0 = 0x58

SER = "Ux983" # Chosse HH983 or Ux983 or Ux943A or Ux981 or Ux94x

DES = "Ux984" # Chosse HH984 or Ux984 or Ux988 or Ux948

MST = 0 # For Ux983 Select 0 for SST and 1 for MST mode

DP0 = 1 # For Ux984 Enable DPTX port0 diagnostics

DP1 = 0 # For Ux984 Enable DPTX port1 diagnostics

##################Keep Always ON#############################

VP = 1 # Enable VP diagnostics

SER_MSAs = 1 # Dump 983 SER MSAs

DTGs = 1 # dump DES DTGs

DPRX = 1 # Enable 983 DPRX diagnostics

DPTX = 1 # Enable 984 DPTX diagnostics

#############################################################

def apb_read_reg(DevAddrRxMain, addr16b):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

board.WriteI2C(DevAddrRxMain, APB_ADR0, addr16b_lsb)

board.WriteI2C(DevAddrRxMain, APB_ADR1, addr16b_msb)

board.WriteI2C(DevAddrRxMain, APB_CTL, 0x03)

apbData0 = board.ReadI2C(DevAddrRxMain, APB_DATA0)

apbData1 = board.ReadI2C(DevAddrRxMain, APB_DATA1)

apbData2 = board.ReadI2C(DevAddrRxMain, APB_DATA2)

apbData3 = board.ReadI2C(DevAddrRxMain, APB_DATA3)

apbData = (apbData3 << 24) | (apbData2 << 16) | (apbData1 << 8) | (apbData0 << 0)

val32bit = apbData

return val32bit

def apb_write_reg(DevAddrRxMain, addr16b, data32b):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

board.WriteI2C(DevAddrRxMain, APB_ADR0, addr16b_lsb)

board.WriteI2C(DevAddrRxMain, APB_ADR1, addr16b_msb)

# print 'data32b', data32b

apbData0 = int((data32b & 0x000000FF) >> 0)

# print 'type', type(apbData0), apbData0

apbData1 = int((data32b & 0x0000FF00) >> 8)

apbData2 = int((data32b & 0x00FF0000) >> 16)

apbData3 = int((data32b & 0xFF000000) >> 24)

board.WriteI2C(DevAddrRxMain, APB_DATA0, apbData0)

board.WriteI2C(DevAddrRxMain, APB_DATA1, apbData1)

board.WriteI2C(DevAddrRxMain, APB_DATA2, apbData2)

board.WriteI2C(DevAddrRxMain, APB_DATA3, apbData3)

board.WriteI2C(DevAddrRxMain, APB_CTL, 0x01)

def MSA_apb_read_reg(addr16b, channel, Device_ID):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

if channel == 0:

page = 0x03

elif channel == 1:

page = 0x0B

else:

page = 0x03

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

board.WriteI2C(Device_ID, APB_ADR0, addr16b_lsb)

board.WriteI2C(Device_ID, APB_ADR1, addr16b_msb)

board.WriteI2C(Device_ID, APB_CTL, page)

apbData0 = board.ReadI2C(Device_ID, APB_DATA0)

apbData1 = board.ReadI2C(Device_ID, APB_DATA1)

apbData2 = board.ReadI2C(Device_ID, APB_DATA2)

apbData3 = board.ReadI2C(Device_ID, APB_DATA3)

apbData = (apbData3 << 24) + (apbData2 << 16) + (apbData1 << 8) + (apbData0 << 0)

val32bit = apbData

return val32bit

def Measure_Video_DPTX(desAlias0, Port, PRNT_STATUS):

print("")

Offset = 0x00

htotal = MSA_apb_read_reg(0x180 + Offset, int(Port), desAlias0)

vtotal = MSA_apb_read_reg(0x184 + Offset, int(Port), desAlias0)

hres = MSA_apb_read_reg(0x194 + Offset, int(Port), desAlias0)

vres = MSA_apb_read_reg(0x198 + Offset, int(Port), desAlias0)

hstart = MSA_apb_read_reg(0x19C + Offset, int(Port), desAlias0)

vstart = MSA_apb_read_reg(0x1A0 + Offset, int(Port), desAlias0)

hswidth = MSA_apb_read_reg(0x18C + Offset, int(Port), desAlias0)

vswidth = MSA_apb_read_reg(0x190 + Offset, int(Port), desAlias0)

if PRNT_STATUS == 1:

print("Port", Port, ": DPTX VIDEO RESOLUTION:")

print("Port", Port, ": htotal (0x180) = " + str(htotal))

print("Port", Port, ": vtotal (0x184) = " + str(vtotal))

print("Port", Port, ": hres (0x18C) = " + str(hres))

print("Port", Port, ": vres (0x190) = " + str(vres))

print("Port", Port, ": hstart (0x19C) = " + str(hstart))

print("Port", Port, ": vstart (0x1A0) = " + str(vstart))

print("Port", Port, ": hswidth (0x18C) = " + str(hswidth))

print("Port", Port, ": vswidth (0x18C) = " + str(vswidth))

return htotal, hres, vtotal, vres

def Measure_Video_DPTX_HH(desAlias0, Port, PRNT_STATUS):

print("")

Offset = 0x00

htotal = MSA_apb_read_reg(0x820 + Offset, int(Port), desAlias0)

vtotal = MSA_apb_read_reg(0x824 + Offset, int(Port), desAlias0)

hres = MSA_apb_read_reg(0x834 + Offset, int(Port), desAlias0)

vres = MSA_apb_read_reg(0x838 + Offset, int(Port), desAlias0)

hstart = MSA_apb_read_reg(0x83C + Offset, int(Port), desAlias0)

vstart = MSA_apb_read_reg(0x840 + Offset, int(Port), desAlias0)

hswidth = MSA_apb_read_reg(0x82C + Offset, int(Port), desAlias0)

vswidth = MSA_apb_read_reg(0x830 + Offset, int(Port), desAlias0)

if PRNT_STATUS == 1:

print("Port", Port, ": DPTX VIDEO RESOLUTION:")

print("Port", Port, ": htotal (0x820) = " + str(htotal))

print("Port", Port, ": vtotal (0x824) = " + str(vtotal))

print("Port", Port, ": hres (0x834) = " + str(hres))

print("Port", Port, ": vres (0x838) = " + str(vres))

print("Port", Port, ": hstart (0x83C) = " + str(hstart))

print("Port", Port, ": vstart (0x840) = " + str(vstart))

print("Port", Port, ": hswidth (0x82C) = " + str(hswidth))

print("Port", Port, ": vswidth (0x830) = " + str(vswidth))

return htotal, hres, vtotal, vres

def apb_read_reg_984_DPTX(addr16b, channel, Device_ID):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

if channel == 0:

page = 0x03

elif channel == 1:

page = 0x0B

else:

page = 0x03

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

##print 'READ inst'

board.WriteI2C(Device_ID, APB_ADR0, addr16b_lsb)

board.WriteI2C(Device_ID, APB_ADR1, addr16b_msb)

board.WriteI2C(Device_ID, APB_CTL, page)

apbData0 = board.ReadI2C(Device_ID, APB_DATA0)

apbData1 = board.ReadI2C(Device_ID, APB_DATA1)

apbData2 = board.ReadI2C(Device_ID, APB_DATA2)

apbData3 = board.ReadI2C(Device_ID, APB_DATA3)

apbData = (apbData3 << 24) + (apbData2 << 16) + (apbData1 << 8) + (apbData0 << 0)

val32bit = apbData

Device_ID = 0x00

return val32bit

def Ux984_APB_Dump(Port,Device_RX):

Stream = 0 # 0, 1, 2, or 3

if Stream == 0 :

Offset = 0x00

elif Stream == 1:

Offset = 0x400

elif Stream == 2:

Offset = 0x420

elif Stream == 3:

Offset = 0x500

else:

Offset = 0x00

print "PORT ",Port," DPTX APB Dump: Main Stream Attributes"

REG_000= apb_read_reg_984_DPTX(0x000,int(Port), Device_RX )

print "REG_000 (LINK_BW_SET) = ", (REG_000)

REG_004= apb_read_reg_984_DPTX(0x004,int(Port), Device_RX )

print "REG_004 (LANE_COUNT_SET) = ", (REG_004)

REG_008= apb_read_reg_984_DPTX(0x008,int(Port), Device_RX )

print "REG_008 (ENHANCED_FRAME_EN) = ", (REG_008)

REG_00C= apb_read_reg_984_DPTX(0x00C,int(Port), Device_RX )

print "REG_00C (TRAINING_PATTERN_SET) = ", (REG_00C)

REG_010= apb_read_reg_984_DPTX(0x010,int(Port), Device_RX )

print "REG_010 (LINK_QUAL_PATTERN_SET) = ", (REG_010)

REG_014= apb_read_reg_984_DPTX(0x014,int(Port), Device_RX )

print "REG_014 (SCRAMBLING_DISABLE) = ", (REG_014)

REG_018= apb_read_reg_984_DPTX(0x018,int(Port), Device_RX )

print "REG_018 (DOWNSPREAD_CTRL) = ", (REG_018)

REG_01C= apb_read_reg_984_DPTX(0x01C,int(Port), Device_RX )

print "REG_01C (EDP_CAPABILITY_CONFIG) = ", (REG_01C)

REG_020= apb_read_reg_984_DPTX(0x020,int(Port), Device_RX )

print "REG_020 (HBR2_COMPLIANCE_SCRAMBLER_RESET) = ", (REG_020)

REG_024= apb_read_reg_984_DPTX(0x024,int(Port), Device_RX )

print "REG_024 (DISPLAYPORT_VERSION) = ", (REG_024)

REG_028= apb_read_reg_984_DPTX(0x028,int(Port), Device_RX )

print "REG_024 (PHY_POWER_STATE) = ", (REG_028)

REG_02C= apb_read_reg_984_DPTX(0x02C,int(Port), Device_RX )

print "REG_02C (LANE_REMAP_CONTROL) = ", (REG_02C)

REG_030= apb_read_reg_984_DPTX(0x030,int(Port), Device_RX )

print "REG_030 (CUSTOM_80BIT_PATTERN_0) = ", (REG_030)

REG_034= apb_read_reg_984_DPTX(0x034,int(Port), Device_RX )

print "REG_034 (CUSTOM_80BIT_PATTERN_1) = ", (REG_034)

REG_038= apb_read_reg_984_DPTX(0x038,int(Port), Device_RX )

print "REG_038 (CUSTOM_80BIT_PATTERN_2) = ", (REG_038)

REG_060= apb_read_reg_984_DPTX(0x060,int(Port), Device_RX )

print "REG_060 (FEC_ENABLE) = ", (REG_060)

REG_080= apb_read_reg_984_DPTX(0x080,int(Port), Device_RX )

print "REG_080 (TRANSMITTER_OUTPUT_ENABLE) = ", (REG_080)

REG_084= apb_read_reg_984_DPTX(0x084,int(Port), Device_RX )

print "REG_084 (VIDEO_STREAM_ENABLE) = ", (REG_084)

REG_088= apb_read_reg_984_DPTX(0x088,int(Port), Device_RX )

print "REG_088 (SECONDARY_STREAM_ENABLE) = ", (REG_088)

REG_08C= apb_read_reg_984_DPTX(0x08C,int(Port), Device_RX )

print "REG_088 (SECONDARY_DATA_WINDOW) = ", (REG_08C)

REG_090= apb_read_reg_984_DPTX(0x090,int(Port), Device_RX )

print "REG_090 (SOFT_RESET) = ", (REG_090)

REG_094= apb_read_reg_984_DPTX(0x094,int(Port), Device_RX )

print "REG_094 (INPUT_SOURCE_ENABLE) = ", (REG_094)

REG_098= apb_read_reg_984_DPTX(0x098,int(Port), Device_RX )

print "REG_098 (FEC_ENABLE) = ", (REG_098)

REG_0C0= apb_read_reg_984_DPTX(0x0C0,int(Port), Device_RX )

print "REG_0C0 (ORCE_SCRAMBLER_RESET) = ", (REG_0C0)

REG_0C4= apb_read_reg_984_DPTX(0x0C4,int(Port), Device_RX )

print "REG_0C4 (USER_CONTROL_STATUS) = ", (REG_0C4)

REG_0C8= apb_read_reg_984_DPTX(0x0C8,int(Port), Device_RX )

print "REG_0C8 (USER_DATA_CONTROL) = ", (REG_0C8)

REG_0F8= apb_read_reg_984_DPTX(0x0F8,int(Port), Device_RX )

print "REG_0F8 (CORE_CAPABILITIES) = ", (REG_0F8)

REG_0FC= apb_read_reg_984_DPTX(0x0FC,int(Port), Device_RX )

print "REG_0FC (CORE_ID) = ", (REG_0FC)

REG_100= apb_read_reg_984_DPTX(0x100,int(Port), Device_RX )

print "REG_100 (AUX_COMMAND) = ", (REG_100)

REG_104= apb_read_reg_984_DPTX(0x104,int(Port), Device_RX )

print "REG_104 (AUX_WRITE_FIFO) = ", (REG_104)

REG_108= apb_read_reg_984_DPTX(0x108,int(Port), Device_RX )

print "REG_108 (AUX_ADDRESS) = ", (REG_108)

REG_10C= apb_read_reg_984_DPTX(0x10C,int(Port), Device_RX )

print "REG_10C (AUX_CLOCK_DIVIDER) = ", (REG_10C)

REG_110= apb_read_reg_984_DPTX(0x110,int(Port), Device_RX )

print "REG_110 (AUX_REPLY_TIMEOUT_INTERVAL) = ", (REG_110)

REG_128= apb_read_reg_984_DPTX(0x128,int(Port), Device_RX )

print "REG_128 (SINK_HPD_STATE) = ", (REG_128)

REG_130= apb_read_reg_984_DPTX(0x130,int(Port), Device_RX )

print "REG_130 (INTERRUPT_STATE) = ", (REG_130)

REG_134= apb_read_reg_984_DPTX(0x134,int(Port), Device_RX )

print "REG_134 (AUX_REPLY_DATA) = ", (REG_134)

REG_138= apb_read_reg_984_DPTX(0x138,int(Port), Device_RX )

print "REG_138 (AUX_REPLY_CODE) = ", (REG_138)

REG_13C= apb_read_reg_984_DPTX(0x13C,int(Port), Device_RX )

print "REG_13C (AUX_REPLY_COUNT) = ", (REG_13C)

REG_140= apb_read_reg_984_DPTX(0x140,int(Port), Device_RX )

print "REG_140 (INTERRUPT_STATUS) = ", (REG_140)

REG_144= apb_read_reg_984_DPTX(0x144,int(Port), Device_RX )

print "REG_144 (INTERRUPT_MASK) = ", (REG_144)

REG_148= apb_read_reg_984_DPTX(0x148,int(Port), Device_RX )

print "REG_148 (REPLY_DATA_COUNT) = ", (REG_148)

REG_14C= apb_read_reg_984_DPTX(0x14C,int(Port), Device_RX )

print "REG_14C (AUX_STATUS) = ", (REG_14C)

REG_150= apb_read_reg_984_DPTX(0x150,int(Port), Device_RX )

print "REG_150 (AUX_REPLY_CLOCK_WIDTH) = ", (REG_150)

REG_154= apb_read_reg_984_DPTX(0x154,int(Port), Device_RX )

print "REG_154 (AUX_WAKE_ACK_DETECTED) = ", (REG_154)

REG_158= apb_read_reg_984_DPTX(0x158,int(Port), Device_RX )

print "REG_158 (GP_HOST_TIMER) = ", (REG_158)

print ""

print "STREAM: ", Stream, " Register Read: "

print ""

REG_0180= apb_read_reg_984_DPTX(0x180+Offset,int(Port), Device_RX )

print "REG_0180 (MAIN_STREAM_HTOTAL) = ", (REG_0180)

REG_0184= apb_read_reg_984_DPTX(0x184+Offset,int(Port), Device_RX )

print "REG_0184 (MAIN_STREAM_VTOTAL) = ", (REG_0184)

REG_0188= apb_read_reg_984_DPTX(0x188+Offset,int(Port), Device_RX )

print "REG_0188 (MAIN_STREAM_POLARITY) = ", (REG_0188)

REG_018C= apb_read_reg_984_DPTX(0x18C+Offset,int(Port), Device_RX )

print "REG_018C (MAIN_STREAM_HSWIDTH) = ", (REG_018C)

REG_0190= apb_read_reg_984_DPTX(0x190+Offset,int(Port), Device_RX )

print "REG_0190 (MAIN_STREAM_VSWIDTH) = ", (REG_0190)

REG_0194= apb_read_reg_984_DPTX(0x194+Offset,int(Port), Device_RX )

print "REG_0194 (MAIN_STREAM_HRES) = ", (REG_0194)

REG_0198= apb_read_reg_984_DPTX(0x198+Offset,int(Port), Device_RX )

print "REG_0198 (MAIN_STREAM_VRES) = ", (REG_0198)

REG_019C= apb_read_reg_984_DPTX(0x19C+Offset,int(Port), Device_RX )

print "REG_019C (MAIN_STREAM_HSTART) = ", (REG_019C)

REG_01A0= apb_read_reg_984_DPTX(0x1A0+Offset,int(Port), Device_RX )

print "REG_01A0 (MAIN_STREAM_VSTART) = ", (REG_01A0)

REG_01A4= apb_read_reg_984_DPTX(0x1A4+Offset,int(Port), Device_RX )

print "REG_01A4 (MAIN_STREAM_MISC0) = ", (REG_01A4)

REG_01A8= apb_read_reg_984_DPTX(0x1A8+Offset,int(Port), Device_RX )

print "REG_01A8 (MAIN_STREAM_MISC1) = ", (REG_01A8)

REG_01AC= apb_read_reg_984_DPTX(0x1AC+Offset,int(Port), Device_RX )

print "REG_01AC (MVID) = ", (REG_01AC)

REG_01B0= apb_read_reg_984_DPTX(0x1B0+Offset,int(Port), Device_RX )

print "REG_01B0 (TRANSFER_UNIT_CONFIG_SRC_0) = ", (REG_01B0)

REG_01B4= apb_read_reg_984_DPTX(0x1B4+Offset,int(Port), Device_RX )

print "REG_01B4 (NVID) = ", (REG_01B4)

REG_01B8= apb_read_reg_984_DPTX(0x1B8+Offset,int(Port), Device_RX )

print "REG_01B8 (USER_PIXEL_COUNT) = ", (REG_01B8)

REG_01BC= apb_read_reg_984_DPTX(0x1BC+Offset,int(Port), Device_RX )

print "REG_01BC (USER_DATA_COUNT) = ", (REG_01BC)

REG_01C0= apb_read_reg_984_DPTX(0x1C0+Offset,int(Port), Device_RX )

print "REG_01C0 (MAIN_STREAM_INTERLACED) = ", (REG_01C0)

REG_01C4= apb_read_reg_984_DPTX(0x1C4+Offset,int(Port), Device_RX )

print "REG_01C4 (USER_SYNC_POLARITY) = ", (REG_01C4)

REG_01C8= apb_read_reg_984_DPTX(0x1C8+Offset,int(Port), Device_RX )

print "REG_01C8 (USER_CONTROL) = ", (REG_01C8)

REG_01CC= apb_read_reg_984_DPTX(0x1CC+Offset,int(Port), Device_RX )

print "REG_01CC (USER_CONTROL) = ", (REG_01CC)

REG_0500= apb_read_reg_984_DPTX(0x500,int(Port), Device_RX )

print "REG_0500 (MST_ENABLE) = ", (REG_0500)

REG_0504= apb_read_reg_984_DPTX(0x504,int(Port), Device_RX )

print "REG_0504 (MST_PID_TABLE_INDEX) = ", (REG_0504)

REG_0508= apb_read_reg_984_DPTX(0x504,int(Port), Device_RX )

print "REG_0508 (MST_PID_TABLE_ENTRY) = ", (REG_0508)

REG_050C= apb_read_reg_984_DPTX(0x50C,int(Port), Device_RX )

print "REG_050C (SST_SOURCE_SELECT) = ", (REG_050C)

REG_0510= apb_read_reg_984_DPTX(0x510,int(Port), Device_RX )

print "REG_0510 (MST_ALLOCATION_TRIGGER) = ", (REG_0510)

REG_0514= apb_read_reg_984_DPTX(0x514,int(Port), Device_RX )

print "REG_0514 (MST_PID_TABLE_SELECT) = ", (REG_0514)

REG_0518= apb_read_reg_984_DPTX(0x518,int(Port), Device_RX )

print "REG_0518 (MST_ACTIVE_PAYLOAD_TABLE) = ", (REG_0518)

REG_0520= apb_read_reg_984_DPTX(0x520,int(Port), Device_RX )

print "REG_0520 (MST_ACTIVE) = ", (REG_0520)

REG_0524= apb_read_reg_984_DPTX(0x524,int(Port), Device_RX )

print "REG_0524 (MST_LINK_FRAME_COUNT) = ", (REG_0524)

REG_0528= apb_read_reg_984_DPTX(0x528,int(Port), Device_RX )

print "REG_0528 (MSO_CONFIGURATION) = ", (REG_0528)

REG_0528= apb_read_reg_984_DPTX(0x528,int(Port), Device_RX )

print "REG_0528 (MSO_CONFIGURATION) = ", (REG_0528)

# Port = 1

# print ""

# print "PORT ",Port," DPTX APB Dump: Main Stream Attributes"

# print ""

# REG_000= apb_read_reg(0x000,int(Port), Device_RX )

# print "REG_000 (LINK_BW_SET) = ", (REG_000)

# REG_004= apb_read_reg(0x004,int(Port), Device_RX )

# print "REG_004 (LANE_COUNT_SET) = ", (REG_004)

# REG_008= apb_read_reg(0x008,int(Port), Device_RX )

# print "REG_008 (ENHANCED_FRAME_EN) = ", (REG_008)

# REG_00C= apb_read_reg(0x00C,int(Port), Device_RX )

# print "REG_00C (TRAINING_PATTERN_SET) = ", (REG_00C)

# REG_010= apb_read_reg(0x010,int(Port), Device_RX )

# print "REG_010 (LINK_QUAL_PATTERN_SET) = ", (REG_010)

# REG_014= apb_read_reg(0x014,int(Port), Device_RX )

# print "REG_014 (SCRAMBLING_DISABLE) = ", (REG_014)

# REG_018= apb_read_reg(0x018,int(Port), Device_RX )

# print "REG_018 (DOWNSPREAD_CTRL) = ", (REG_018)

# REG_01C= apb_read_reg(0x01C,int(Port), Device_RX )

# print "REG_01C (EDP_CAPABILITY_CONFIG) = ", (REG_01C)

# REG_020= apb_read_reg(0x020,int(Port), Device_RX )

# print "REG_020 (HBR2_COMPLIANCE_SCRAMBLER_RESET) = ", (REG_020)

# REG_024= apb_read_reg(0x024,int(Port), Device_RX )

# print "REG_024 (DISPLAYPORT_VERSION) = ", (REG_024)

# REG_028= apb_read_reg(0x028,int(Port), Device_RX )

# print "REG_024 (PHY_POWER_STATE) = ", (REG_028)

# REG_02C= apb_read_reg(0x02C,int(Port), Device_RX )

# print "REG_02C (LANE_REMAP_CONTROL) = ", (REG_02C)

# REG_030= apb_read_reg(0x030,int(Port), Device_RX )

# print "REG_030 (CUSTOM_80BIT_PATTERN_0) = ", (REG_030)

# REG_034= apb_read_reg(0x034,int(Port), Device_RX )

# print "REG_034 (CUSTOM_80BIT_PATTERN_1) = ", (REG_034)

# REG_038= apb_read_reg(0x038,int(Port), Device_RX )

# print "REG_038 (CUSTOM_80BIT_PATTERN_2) = ", (REG_038)

# REG_060= apb_read_reg(0x060,int(Port), Device_RX )

# print "REG_060 (FEC_ENABLE) = ", (REG_060)

# REG_080= apb_read_reg(0x080,int(Port), Device_RX )

# print "REG_080 (TRANSMITTER_OUTPUT_ENABLE) = ", (REG_080)

# REG_084= apb_read_reg(0x084,int(Port), Device_RX )

# print "REG_084 (VIDEO_STREAM_ENABLE) = ", (REG_084)

# REG_088= apb_read_reg(0x088,int(Port), Device_RX )

# print "REG_088 (SECONDARY_STREAM_ENABLE) = ", (REG_088)

# REG_08C= apb_read_reg(0x08C,int(Port), Device_RX )

# print "REG_088 (SECONDARY_DATA_WINDOW) = ", (REG_08C)

# REG_090= apb_read_reg(0x090,int(Port), Device_RX )

# print "REG_090 (SOFT_RESET) = ", (REG_090)

# REG_094= apb_read_reg(0x094,int(Port), Device_RX )

# print "REG_094 (INPUT_SOURCE_ENABLE) = ", (REG_094)

# REG_098= apb_read_reg(0x098,int(Port), Device_RX )

# print "REG_098 (FEC_ENABLE) = ", (REG_098)

# REG_0C0= apb_read_reg(0x0C0,int(Port), Device_RX )

# print "REG_0C0 (ORCE_SCRAMBLER_RESET) = ", (REG_0C0)

# REG_0C4= apb_read_reg(0x0C4,int(Port), Device_RX )

# print "REG_0C4 (USER_CONTROL_STATUS) = ", (REG_0C4)

# REG_0C8= apb_read_reg(0x0C8,int(Port), Device_RX )

# print "REG_0C8 (USER_DATA_CONTROL) = ", (REG_0C8)

# REG_0F8= apb_read_reg(0x0F8,int(Port), Device_RX )

# print "REG_0F8 (CORE_CAPABILITIES) = ", (REG_0F8)

# REG_0FC= apb_read_reg(0x0FC,int(Port), Device_RX )

# print "REG_0FC (CORE_ID) = ", (REG_0FC)

# REG_100= apb_read_reg(0x100,int(Port), Device_RX )

# print "REG_100 (AUX_COMMAND) = ", (REG_100)

# REG_104= apb_read_reg(0x104,int(Port), Device_RX )

# print "REG_104 (AUX_WRITE_FIFO) = ", (REG_104)

# REG_108= apb_read_reg(0x108,int(Port), Device_RX )

# print "REG_108 (AUX_ADDRESS) = ", (REG_108)

# REG_10C= apb_read_reg(0x10C,int(Port), Device_RX )

# print "REG_10C (AUX_CLOCK_DIVIDER) = ", (REG_10C)

# REG_110= apb_read_reg(0x110,int(Port), Device_RX )

# print "REG_110 (AUX_REPLY_TIMEOUT_INTERVAL) = ", (REG_110)

# REG_128= apb_read_reg(0x128,int(Port), Device_RX )

# print "REG_128 (SINK_HPD_STATE) = ", (REG_128)

# REG_130= apb_read_reg(0x130,int(Port), Device_RX )

# print "REG_130 (INTERRUPT_STATE) = ", (REG_130)

# REG_134= apb_read_reg(0x134,int(Port), Device_RX )

# print "REG_134 (AUX_REPLY_DATA) = ", (REG_134)

# REG_138= apb_read_reg(0x138,int(Port), Device_RX )

# print "REG_138 (AUX_REPLY_CODE) = ", (REG_138)

# REG_13C= apb_read_reg(0x13C,int(Port), Device_RX )

# print "REG_13C (AUX_REPLY_COUNT) = ", (REG_13C)

# REG_140= apb_read_reg(0x140,int(Port), Device_RX )

# print "REG_140 (INTERRUPT_STATUS) = ", (REG_140)

# REG_144= apb_read_reg(0x144,int(Port), Device_RX )

# print "REG_144 (INTERRUPT_MASK) = ", (REG_144)

# REG_148= apb_read_reg(0x148,int(Port), Device_RX )

# print "REG_148 (REPLY_DATA_COUNT) = ", (REG_148)

# REG_14C= apb_read_reg(0x14C,int(Port), Device_RX )

# print "REG_14C (AUX_STATUS) = ", (REG_14C)

# REG_150= apb_read_reg(0x150,int(Port), Device_RX )

# print "REG_150 (AUX_REPLY_CLOCK_WIDTH) = ", (REG_150)

# REG_154= apb_read_reg(0x154,int(Port), Device_RX )

# print "REG_154 (AUX_WAKE_ACK_DETECTED) = ", (REG_154)

# REG_158= apb_read_reg(0x158,int(Port), Device_RX )

# print "REG_158 (GP_HOST_TIMER) = ", (REG_158)

print ""

print "STREAM: ", Stream, " Register Read: "

print ""

REG_0180= apb_read_reg_984_DPTX(0x180+Offset,int(Port), Device_RX )

print "REG_0180 (MAIN_STREAM_HTOTAL) = ", (REG_0180)

REG_0184= apb_read_reg_984_DPTX(0x184+Offset,int(Port), Device_RX )

print "REG_0184 (MAIN_STREAM_VTOTAL) = ", (REG_0184)

REG_0188= apb_read_reg_984_DPTX(0x188+Offset,int(Port), Device_RX )

print "REG_0188 (MAIN_STREAM_POLARITY) = ", (REG_0188)

REG_018C= apb_read_reg_984_DPTX(0x18C+Offset,int(Port), Device_RX )

print "REG_018C (MAIN_STREAM_HSWIDTH) = ", (REG_018C)

REG_0190= apb_read_reg_984_DPTX(0x190+Offset,int(Port), Device_RX )

print "REG_0190 (MAIN_STREAM_VSWIDTH) = ", (REG_0190)

REG_0194= apb_read_reg_984_DPTX(0x194+Offset,int(Port), Device_RX )

print "REG_0194 (MAIN_STREAM_HRES) = ", (REG_0194)

REG_0198= apb_read_reg_984_DPTX(0x198+Offset,int(Port), Device_RX )

print "REG_0198 (MAIN_STREAM_VRES) = ", (REG_0198)

REG_019C= apb_read_reg_984_DPTX(0x19C+Offset,int(Port), Device_RX )

print "REG_019C (MAIN_STREAM_HSTART) = ", (REG_019C)

REG_01A0= apb_read_reg_984_DPTX(0x1A0+Offset,int(Port), Device_RX )

print "REG_01A0 (MAIN_STREAM_VSTART) = ", (REG_01A0)

REG_01A4= apb_read_reg_984_DPTX(0x1A4+Offset,int(Port), Device_RX )

print "REG_01A4 (MAIN_STREAM_MISC0) = ", (REG_01A4)

REG_01A8= apb_read_reg_984_DPTX(0x1A8+Offset,int(Port), Device_RX )

print "REG_01A8 (MAIN_STREAM_MISC1) = ", (REG_01A8)

REG_01AC= apb_read_reg_984_DPTX(0x1AC+Offset,int(Port), Device_RX )

print "REG_01AC (MVID) = ", (REG_01AC)

REG_01B0= apb_read_reg_984_DPTX(0x1B0+Offset,int(Port), Device_RX )

print "REG_01B0 (TRANSFER_UNIT_CONFIG_SRC_0) = ", (REG_01B0)

REG_01B4= apb_read_reg_984_DPTX(0x1B4+Offset,int(Port), Device_RX )

print "REG_01B4 (NVID) = ", (REG_01B4)

REG_01B8= apb_read_reg_984_DPTX(0x1B8+Offset,int(Port), Device_RX )

print "REG_01B8 (USER_PIXEL_COUNT) = ", (REG_01B8)

REG_01BC= apb_read_reg_984_DPTX(0x1BC+Offset,int(Port), Device_RX )

print "REG_01BC (USER_DATA_COUNT) = ", (REG_01BC)

REG_01C0= apb_read_reg_984_DPTX(0x1C0+Offset,int(Port), Device_RX )

print "REG_01C0 (MAIN_STREAM_INTERLACED) = ", (REG_01C0)

REG_01C4= apb_read_reg_984_DPTX(0x1C4+Offset,int(Port), Device_RX )

print "REG_01C4 (USER_SYNC_POLARITY) = ", (REG_01C4)

REG_01C8= apb_read_reg_984_DPTX(0x1C8+Offset,int(Port), Device_RX )

print "REG_01C8 (USER_CONTROL) = ", (REG_01C8)

REG_0500= apb_read_reg_984_DPTX(0x500,int(Port), Device_RX )

print "REG_0500 (MST_ENABLE) = ", (REG_0500)

REG_0504= apb_read_reg_984_DPTX(0x504,int(Port), Device_RX )

print "REG_0504 (MST_PID_TABLE_INDEX) = ", (REG_0504)

REG_0508= apb_read_reg_984_DPTX(0x504,int(Port), Device_RX )

print "REG_0508 (MST_PID_TABLE_ENTRY) = ", (REG_0508)

REG_050C= apb_read_reg_984_DPTX(0x50C,int(Port), Device_RX )

print "REG_050C (SST_SOURCE_SELECT) = ", (REG_050C)

REG_0510= apb_read_reg_984_DPTX(0x510,int(Port), Device_RX )

print "REG_0510 (MST_ALLOCATION_TRIGGER) = ", (REG_0510)

REG_0514= apb_read_reg_984_DPTX(0x514,int(Port), Device_RX )

print "REG_0514 (MST_PID_TABLE_SELECT) = ", (REG_0514)

REG_0518= apb_read_reg_984_DPTX(0x518,int(Port), Device_RX )

print "REG_0518 (MST_ACTIVE_PAYLOAD_TABLE) = ", (REG_0518)

REG_0520= apb_read_reg_984_DPTX(0x520,int(Port), Device_RX )

print "REG_0520 (MST_ACTIVE) = ", (REG_0520)

REG_0524= apb_read_reg_984_DPTX(0x524,int(Port), Device_RX )

print "REG_0524 (MST_LINK_FRAME_COUNT) = ", (REG_0524)

REG_0528= apb_read_reg_984_DPTX(0x528,int(Port), Device_RX )

print "REG_0528 (MSO_CONFIGURATION) = ", (REG_0528)

REG_0528= apb_read_reg_984_DPTX(0x528,int(Port), Device_RX )

print "REG_0528 (MSO_CONFIGURATION) = ", (REG_0528)

def Ux983_APBs(var):

for var in range (0x00,138):

print hex(var*4), hex(apb_read_reg(serAddr,var*4))

for var in range (256,336):

print hex(var*4), hex(apb_read_reg(serAddr,var*4))

for var in range (448,457):

print hex(var*4), hex(apb_read_reg(serAddr,var*4))

for var in range (512,589+1):

print hex(var*4), hex(apb_read_reg(serAddr,var*4))

for var in range (640,760+1):

print hex(var*4), hex(apb_read_reg(serAddr,var*4))

def HH983_APBs():

print("Receiver core config")

print("0x0 (reciver core enable) = " + hex(apb_read_reg(serAddr,0x0)))

print("0x018 (misc_config) = " + hex(apb_read_reg(serAddr,0x018)))

print("0x024 (request_error_count) = " + hex(apb_read_reg(serAddr,0x024)))

print("0x028 (request_count) = " + hex(apb_read_reg(serAddr,0x028)))

print("0x070 (max_lane_count) = " + hex(apb_read_reg(serAddr,0x070)))

print("0x074 (max_link_rate) = " + hex(apb_read_reg(serAddr,0x074)))

print("")

print("PHY config and status")

print("0x208 (phy_status) = " + hex(apb_read_reg(serAddr,0x208)))

print("0x214 (min_voltage_swing) = " + hex(apb_read_reg(serAddr,0x214)))

print("0x218 (min_pre_emphasis) = " + hex(apb_read_reg(serAddr,0x218)))

print("0x208 (phy_status) = " + hex(apb_read_reg(serAddr,0x208)))

print("")

print("DPCD config space")

print("0x400 (LANE01_status) = " + hex(apb_read_reg(serAddr,0x400)))

print("0x404 (LANE23_status) = " + hex(apb_read_reg(serAddr,0x404)))

print("---MSA Video Timings----")

print("H Res: ", apb_read_reg(serAddr,0x500))

print("H Pol: ", apb_read_reg(serAddr,0x504))

hsync = apb_read_reg(serAddr,0x508)

print("H Sync: ", apb_read_reg(serAddr,0x508))

print("H Back Porch: ", apb_read_reg(serAddr,0x50C) - hsync)

print("H Total: ", apb_read_reg(serAddr,0x510))

print("V Res: ", apb_read_reg(serAddr,0x514))

print("V Pol: ", apb_read_reg(serAddr,0x518))

v_sync = apb_read_reg(serAddr,0x51c)

print("V Sync Width: ", v_sync)

print("V Back Porch: ", apb_read_reg(serAddr,0x520) - v_sync)

print("V Total: ", apb_read_reg(serAddr,0x524))

print(" ")

print("MSA MISC0: ", apb_read_reg(serAddr,0x528))

print("MSA_MISC1: ", apb_read_reg(serAddr,0x52C))

print("MSA_MVID: ", hex(apb_read_reg(serAddr,0x530)))

print("MSA_NVID: ", hex(apb_read_reg(serAddr,0x534)))

print("MSA_VBID: ", hex(apb_read_reg(serAddr,0x538)))

print("MSA Updated", apb_read_reg(serAddr,0x544))

print("")

print("HDCP Config")

print("0x600 (HDCP_enable) = " + hex(apb_read_reg(serAddr,0x600)))

print("0x604 (HDCP_mode_select) = " + hex(apb_read_reg(serAddr,0x604)))

# print("0x608 (HDCP_KS_31_0) = " + hex(apb_read_reg(serAddr,0x608)))

# print("0x60C (HDCP_KS_63_32) = " + hex(apb_read_reg(serAddr,0x60C)))

# print("0x610 (HDCP_KM_31_0) = " + hex(apb_read_reg(serAddr,0x610)))

# print("0x614 (HDCP_KM_55_32) = " + hex(apb_read_reg(serAddr,0x614)))

print("0x618 (HDCP_AN_31_0) = " + hex(apb_read_reg(serAddr,0x618)))

print("0x61C (HDCP_AN_63_32) = " + hex(apb_read_reg(serAddr,0x61C)))

print("0x624 (HDCP_authentication_in_progress) = " + hex(apb_read_reg(serAddr,0x624)))

print("0x628 (HDCP_status) = " + hex(apb_read_reg(serAddr,0x628)))

print("0x62C (HDCP_CIPHER_CONTROL) = " + hex(apb_read_reg(serAddr,0x62C)))

print("0x630 (HDCP_AKSV_31_0) = " + hex(apb_read_reg(serAddr,0x630)))

print("0x634 (HDCP_AKSV_63_32) = " + hex(apb_read_reg(serAddr,0x634)))

print("0x638 (HDCP_HW_BKSV_31_0) = " + hex(apb_read_reg(serAddr,0x638)))

print("0x63C (HDCP_HW_BKSV_63_32) = " + hex(apb_read_reg(serAddr,0x63C)))

print("0x650 (HDCP_REPEATER) = " + hex(apb_read_reg(serAddr,0x650)))

print("0x654 (HDCP_stream_cipher_enable) = " + hex(apb_read_reg(serAddr,0x654)))

print("0x658 (HDCP_MO_31_0) = " + hex(apb_read_reg(serAddr,0x658)))

print("0x65C (HDCP_MO_63_32) = " + hex(apb_read_reg(serAddr,0x65C)))

print("0x660 (HDCP_AES_INPUT_SELECT) = " + hex(apb_read_reg(serAddr,0x660)))

print("0x664 (HDCP_AES_COUNTER_DISABLE) = " + hex(apb_read_reg(serAddr,0x664)))

print("0x668 (HDCP_AES_COUNTER_ADVANCE) = " + hex(apb_read_reg(serAddr,0x668)))

print("0x66C (HDCP_ENCRYPTION_CONTROL_FIELD_31_0) = " + hex(apb_read_reg(serAddr,0x66C)))

print("0x670 (HDCP_ENCRYPTION_CONTROL_FIELD_63_32) = " + hex(apb_read_reg(serAddr,0x670)))

print("0x678 (HDCP_RN_31_0) = " + hex(apb_read_reg(serAddr,0x678)))

print("0x67C (HDCP_RN_63_32) = " + hex(apb_read_reg(serAddr,0x67C)))

print("0x684 (HDCP_RNG_CIPHER_AN_31_0) = " + hex(apb_read_reg(serAddr,0x684)))

print("0x688 (HDCP_RNG_CIPHER_AN_63_32) = " + hex(apb_read_reg(serAddr,0x688)))

print("0x68C (HDCP_HOST_TIMER) = " + hex(apb_read_reg(serAddr,0x68C)))

print("0x690 (HDCP_encryption_active) = " + hex(apb_read_reg(serAddr,0x690)))

print("0x694 (HDCP_link_integrity_failure) = " + hex(apb_read_reg(serAddr,0x694)))

print("0x698 (HDCP_content_type_select_31_0) = " + hex(apb_read_reg(serAddr,0x698)))

print("0x69C (HDCP_content_type_select_63_32) = " + hex(apb_read_reg(serAddr,0x69C)))

def Ux948_Res_dump(desAlias0):

time.sleep(1)

board.WriteI2C(desAlias0,0x68,0x19) # H active High monitor

Hhigh = board.ReadI2C(desAlias0, 0x69, 1)

board.WriteI2C(desAlias0,0x68,0x09) # H active Low monitor

Hlow = board.ReadI2C(desAlias0, 0x69, 1)

board.WriteI2C(desAlias0,0x68,0x39) # V active High monitor

Vhigh = board.ReadI2C(desAlias0, 0x69, 1)

board.WriteI2C(desAlias0,0x68,0x29) # V active Low monitor

Vlow = board.ReadI2C(desAlias0, 0x69, 1)

mask = int('00111111',2)

hlowmask = Hlow & mask

hhighmask = Hhigh & mask

vlowmask = Vlow & mask

vhighmask = Vhigh & mask

hhighmask = hhighmask << 6

vhighmask = vhighmask << 6

Hactive = hhighmask | hlowmask

Vactive = vhighmask | vlowmask

print Hactive ,"x", Vactive ,",", #print out detected Dimensions

def Ux98x_SERDES_Full_Diagnostics():

time.sleep(0.1)

if SER == "HH983" or SER == "Ux983" or SER == "Ux943A":

board.WriteI2C(serAddr, 0x7, 0x88) # Enable I2C Passthrough for FPD4 98x SER

if SER == "Hx94x":

board.WriteI2C(serAddr, 0x3, 0xDA) # Enable I2C Passthrough for FPD4 98x SER

if SER == "Ux94x":

print"Ux94x Statuses"

for x in range(20):

print"Device_ID = ", hex(board.ReadI2C(serAddr, 0x0)), ",",

print"GENERAL_STATUS = ", hex(board.ReadI2C(serAddr, 0xC))

# Clear CRC Erorr"

Reg_4 = board.ReadI2C(serAddr, 0x4)

Reg_4_mask = Reg_4 | 0x20

board.WriteI2C(serAddr, 0x4, Reg_4_mask) # CRC Error Reset

Reg_4 = board.ReadI2C(serAddr, 0x4)

Reg_4_unmask = Reg_4 & 0xDF

board.WriteI2C(serAddr, 0x4, Reg_4_unmask) # CRC Error Reset Clear

for x in range(20):

print"CRC_0xA = ", hex(board.ReadI2C(serAddr, 0xA)), ",",

print"CRC_0xB = ", hex(board.ReadI2C(serAddr, 0xB))

if DES == "Ux948":

print "Ux948 Statuses"

for x in range(20):

print"GENERAL_STATUS = ", hex(board.ReadI2C(desAlias0, 0x1C)), ",",

print"DUAL_RX_CTL = ", hex(board.ReadI2C(desAlias0, 0x34)), ",",

print"Mode_Sel = ", hex(board.ReadI2C(desAlias0, 0x37)), ",",

Ux948_Res_dump(desAlias0)

print"FPD_TX_MODE = ", hex(board.ReadI2C(desAlias0, 0x49))

if SER == "HH983" or SER == "Ux983" or SER == "Ux943A" or SER == "Ux981":

print"----------------------------------"

print("Lock / Link Status")

for x in range(10):

print"Ser Reg 0xC = ", hex(board.ReadI2C(serAddr, 0xC, 1)), ",",

print"Des Reg 0x53 = ", hex(board.ReadI2C(desAlias0, 0x53, 1)), ",",

print"Des Reg 0x54 = ", hex(board.ReadI2C(desAlias0, 0x54, 1)), ",",

board.WriteI2C(serAddr, 0x40, 18 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x4E)

print"Des Reg 0x4E = ", hex(board.ReadI2C(desAlias0, 0x42))

if VP and SER == "HH983" or SER == "Ux983" or SER == "Ux943A" or SER == "Ux981":

print "----------------------------------"

print ("VP Status")

for x in range(10):

board.WriteI2C(serAddr, 0x40, 0x33)

board.WriteI2C(serAddr, 0x41, 0x30)

print "VP_STATUS:", board.ReadI2C(serAddr, 0x42, 1), ",",

board.WriteI2C(serAddr, 0x40, 0x33)

board.WriteI2C(serAddr, 0x41, 0x31)

print "VP_INTERRUPTS:", board.ReadI2C(serAddr, 0x42, 1)

if SER == "Ux981":

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0xe)

read_val = board.ReadI2C(serAddr, 0x42)

print"INTR_STS_DPHY = 0x", hex(read_val)

print"[1] IS_DPHY_LANE_SYNC_ERROR", (read_val & 0x2) >> 1

print"[0] IS_DPHY_LANE_ERROR", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0xf)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_STATUS = 0x", hex(read_val)

print"[4] C_LANE_ACTIVE", (read_val & 0x10) >> 4

print"[3] D_LANE3_ACTIVE", (read_val & 0x8) >> 3

print"[2] D_LANE2_ACTIVE", (read_val & 0x4) >> 2

print"[1] D_LANE1_ACTIVE", (read_val & 0x2) >> 1

print"[0] D_LANE0_ACTIVE", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x10)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_DLANE0 = 0x", hex(read_val)

print"[4] EOT_SYNC_ERROR", (read_val & 0x10) >> 4

print"[3] SOT_ERROR", (read_val & 0x8) >> 3

print"[2] SOT_SYNC_ERROR", (read_val & 0x4) >> 2

print"[1] CNTRL_ERR_HSRQST", (read_val & 0x2) >> 1

print"[0] HS_RX_TO_ERROR", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x11)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_DLANE1 = 0x", hex(read_val)

print"[4] EOT_SYNC_ERROR", (read_val & 0x10) >> 4

print"[3] SOT_ERROR", (read_val & 0x8) >> 3

print"[2] SOT_SYNC_ERROR", (read_val & 0x4) >> 2

print"[1] CNTRL_ERR_HSRQST", (read_val & 0x2) >> 1

print"[0] HS_RX_TO_ERROR", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x12)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_DLANE2 = 0x", hex(read_val)

print"[4] EOT_SYNC_ERROR", (read_val & 0x10) >> 4

print"[3] SOT_ERROR", (read_val & 0x8) >> 3

print"[2] SOT_SYNC_ERROR", (read_val & 0x4) >> 2

print"[1] CNTRL_ERR_HSRQST", (read_val & 0x2) >> 1

print"[0] HS_RX_TO_ERROR", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x13)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_DLANE3 = 0x", hex(read_val)

print"[4] EOT_SYNC_ERROR", (read_val & 0x10) >> 4

print"[3] SOT_ERROR", (read_val & 0x8) >> 3

print"[2] SOT_SYNC_ERROR", (read_val & 0x4) >> 2

print"[1] CNTRL_ERR_HSRQST", (read_val & 0x2) >> 1

print"[0] HS_RX_TO_ERROR", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x14)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_ERR_CLK_LANE = 0x", hex(read_val)

print

"[2] CNTRL_ERR_HSRQST_CLK", (read_val & 0x4) >> 2

print"[0] HS RX TO ERROR_CLK", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x15)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_SYNC_STS = 0x", read_val

print"[3] DLANE3_SYNC_STS", (read_val & 0x8) >> 3

print"[2] DLANE2_SYNC_STS", (read_val & 0x4) >> 2

print"[1] DLANE1_SYNC_STS", (read_val & 0x2) >> 1

print"[0] DLANE0_SYNC_STS", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x23)

read_val = board.ReadI2C(serAddr, 0x42)

print"INTR_STS_DSI_ERR = 0x", read_val

print"[7] IS_INV_TYPE_GLW_ERR", (read_val & 0x80) >> 7

print"[6] IS_INV_WC_GLW_ERR", (read_val & 0x40) >> 6

print"[5] IS_INV_LEN_ERR", (read_val & 0x20) >> 5

print"[4] IS_INV_VC_ERR", (read_val & 0x10) >> 4

print"[3] IS_INV_DT_ERR", (read_val & 0x8) >> 3

print"[2] IS_CHECKSUM_ERR", (read_val & 0x4) >> 2

print"[1] IS_ECC_MULTI_ERR", (read_val & 0x2) >> 1

print"[0] IS_ECC_SINGLE_ERR", read_val & 0x1

board.WriteI2C(serAddr, 0x40, 4 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x2a)

read_val = board.ReadI2C(serAddr, 0x42)

print"DPHY_DSI_VC_DTYPE = 0x", read_val

if SER == "HH983" and DPRX:

print "----------------------------------"

print ("DPRX Status")

apb_write_reg(serAddr, 0x4F4, 0x00) # Address [19:16]

apb_write_reg(serAddr, 0x4F0, 0x03)

apb_write_reg(serAddr, 0x4F4, 0x01) # Address [15:8]

apb_write_reg(serAddr, 0x4F0, 0x03)

apb_write_reg(serAddr, 0x4F4, 0x00) # Address [7:0]

apb_write_reg(serAddr, 0x4F0, 0x03)

apb_write_reg(serAddr, 0x4F0, 0x02) # Read Strobe

LINK_BW_SET = apb_read_reg(serAddr, 0x4F8)

if LINK_BW_SET == 0:

print "No Link Speed Detected"

elif LINK_BW_SET == 0x06:

print "Link Rate = 1.62Gbps/lane"

elif LINK_BW_SET == 0x0A:

print "Link Rate = 2.7Gbps/lane"

elif LINK_BW_SET == 0x14:

print "Link Rate = 5.4Gbps/lane"

elif LINK_BW_SET == 0x1E:

print "Link Rate = 8.1Gbps/lane"

# Lane Count Check via Direct DPCD Access

apb_write_reg(serAddr, 0x4F4, 0x00) # Address [19:16]

apb_write_reg(serAddr, 0x4F0, 0x03)

apb_write_reg(serAddr, 0x4F4, 0x01) # Address [15:8]

apb_write_reg(serAddr, 0x4F0, 0x03)

apb_write_reg(serAddr, 0x4F4, 0x01) # Address [7:0]

apb_write_reg(serAddr, 0x4F0, 0x03)

apb_write_reg(serAddr, 0x4F0, 0x02) # Read Strobe

LANE_COUNT_SET = apb_read_reg(serAddr, 0x4F8)

if LANE_COUNT_SET & 0x1F == 0:

print "No Active DP Lanes Detected"

elif LANE_COUNT_SET & 0x1F == 0x01:

print "One DP Lane"

elif LANE_COUNT_SET & 0x1F == 0x02:

print "Two DP Lanes"

elif LANE_COUNT_SET & 0x1F == 0x04:

print "4 DP Lanes"

print("H Res")

print apb_read_reg(serAddr, 0x500)

print("H POL")

print apb_read_reg(serAddr, 0x504)

print("H SYNC WIDTH")

h_sync = apb_read_reg(serAddr, 0x508)

print h_sync

print("H BACK PORCH")

H_Back = apb_read_reg(serAddr, 0x50C) - h_sync

print H_Back

print("H TOTAL")

print apb_read_reg(serAddr, 0x510)

print("V Res")

print apb_read_reg(serAddr, 0x514)

print("V POL")

print apb_read_reg(serAddr, 0x518)

print("V SYNC WIDTH")

v_sync = apb_read_reg(serAddr, 0x51C)

print v_sync

print("V BACK PORCH ")

v_back = apb_read_reg(serAddr, 0x520) - v_sync

print v_back

print("HV TOTAL")

print apb_read_reg(serAddr, 0x524)

print("MSA_MISC0")

print apb_read_reg(serAddr, 0x528)

print("MSA_MISC1")

print apb_read_reg(serAddr, 0x52C)

print("MSA_MVID")

print apb_read_reg(serAddr, 0x530)

print("MSA_NVID")

print apb_read_reg(serAddr, 0x534)

print("MSA_VBID")

print apb_read_reg(serAddr, 0x538)

if SER == "Ux983" or SER == "Ux943A":

print "----------------------------------"

print ("DPRX Status")

print apb_read_reg(serAddr, 0x400) * 27, ("Rate")

print apb_read_reg(serAddr, 0x404), ("Lanes")

print hex(apb_read_reg(serAddr, 0x43c))

print hex(apb_read_reg(serAddr, 0x440))

print hex(apb_read_reg(serAddr, 0x18))

print hex(apb_read_reg(serAddr, 0x48C))

if apb_read_reg(serAddr, 0x48C) == 0:

print "Video source is set to SST mode"

if apb_read_reg(serAddr, 0x48C) == 1:

print "Video source is set to MST mode"

print "----------------------------------"

if SER == "Ux983" or SER == "Ux943A" and SER_MSAs:

if MST == 0:

apb_write_reg(serAddr, 0x540, 0x0)

print("H Res")

print apb_read_reg(serAddr, 0x500)

print("H POL")

print apb_read_reg(serAddr, 0x504)

print("H SYNC WIDTH")

h_sync = apb_read_reg(serAddr, 0x508)

print h_sync

print("H BACK PORCH")

H_Back = apb_read_reg(serAddr, 0x50C) - h_sync

print H_Back

print("H TOTAL")

print apb_read_reg(serAddr, 0x510)

print("V Res")

print apb_read_reg(serAddr, 0x514)

print("V POL")

print apb_read_reg(serAddr, 0x518)

print("V SYNC WIDTH")

v_sync = apb_read_reg(serAddr, 0x51C)

print v_sync

print("V BACK PORCH ")

v_back = apb_read_reg(serAddr, 0x520) - v_sync

print v_back

print("HV TOTAL")

print apb_read_reg(serAddr, 0x524)

print("MSA_MISC0")

print apb_read_reg(serAddr, 0x528)

print("MSA_MISC1")

print apb_read_reg(serAddr, 0x52C)

print("MSA_MVID")

print apb_read_reg(serAddr, 0x530)

print("MSA_NVID")

print apb_read_reg(serAddr, 0x534)

print("MSA_VBID")

print apb_read_reg(serAddr, 0x538)

print("SYMBOL ERRORs - Lane 0")

print hex(apb_read_reg(serAddr, 0x490))

print("SYMBOL ERRORs - Lane 1")

print hex(apb_read_reg(serAddr, 0x494))

print("SYMBOL ERRORs - Lane 2")

print hex(apb_read_reg(serAddr, 0x498))

print("SYMBOL ERRORs - Lane 3")

print hex(apb_read_reg(serAddr, 0x49C))

else:

print "----------------------------------"

print("## MST0")

apb_write_reg(serAddr, 0x540, 0x0)

print("H Res")

print apb_read_reg(serAddr, 0x500)

print("H POL")

print apb_read_reg(serAddr, 0x504)

print("H SYNC WIDTH")

h_sync = apb_read_reg(serAddr, 0x508)

print h_sync

print("H BACK PORCH")

H_Back = apb_read_reg(serAddr, 0x50C) - h_sync

print H_Back

print("H TOTAL")

print apb_read_reg(serAddr, 0x510)

print("V Res")

print apb_read_reg(serAddr, 0x514)

print("V POL")

print apb_read_reg(serAddr, 0x518)

print("V SYNC WIDTH")

v_sync = apb_read_reg(serAddr, 0x51C)

print v_sync

print("V BACK PORCH ")

v_back = apb_read_reg(serAddr, 0x520) - v_sync

print v_back

print("HV TOTAL")

print apb_read_reg(serAddr, 0x524)

print("MSA_MISC0")

print apb_read_reg(serAddr, 0x528)

print("MSA_MISC1")

print apb_read_reg(serAddr, 0x52C)

print("MSA_MVID")

print apb_read_reg(serAddr, 0x530)

print("MSA_NVID")

print apb_read_reg(serAddr, 0x534)

print("MSA_VBID")

print apb_read_reg(serAddr, 0x538)

print("SYMBOL ERRORs - Lane 0")

print hex(apb_read_reg(serAddr, 0x490))

print("SYMBOL ERRORs - Lane 1")

print hex(apb_read_reg(serAddr, 0x494))

print("SYMBOL ERRORs - Lane 2")

print hex(apb_read_reg(serAddr, 0x498))

print("SYMBOL ERRORs - Lane 3")

print hex(apb_read_reg(serAddr, 0x49C))

print("## MST1")

apb_write_reg(serAddr, 0x540, 0x1)

print("H Res")

print apb_read_reg(serAddr, 0x500)

print("H POL")

print apb_read_reg(serAddr, 0x504)

print("H SYNC WIDTH")

h_sync = apb_read_reg(serAddr, 0x508)

print h_sync

print("H BACK PORCH")

H_Back = apb_read_reg(serAddr, 0x50C) - h_sync

print H_Back

print("H TOTAL")

print apb_read_reg(serAddr, 0x510)

print("V Res")

print apb_read_reg(serAddr, 0x514)

print("V POL")

print apb_read_reg(serAddr, 0x518)

print("V SYNC WIDTH")

v_sync = apb_read_reg(serAddr, 0x51C)

print v_sync

print("V BACK PORCH ")

v_back = apb_read_reg(serAddr, 0x520) - v_sync

print v_back

print("HV TOTAL")

print apb_read_reg(serAddr, 0x524)

print("MSA_MISC0")

print apb_read_reg(serAddr, 0x528)

print("MSA_MISC1")

print apb_read_reg(serAddr, 0x52C)

print("MSA_MVID")

print apb_read_reg(serAddr, 0x530)

print("MSA_NVID")

print apb_read_reg(serAddr, 0x534)

print("MSA_VBID")

print apb_read_reg(serAddr, 0x538)

print("SYMBOL ERRORs - Lane 0")

print hex(apb_read_reg(serAddr, 0x490))

print("SYMBOL ERRORs - Lane 1")

print hex(apb_read_reg(serAddr, 0x494))

print("SYMBOL ERRORs - Lane 2")

print hex(apb_read_reg(serAddr, 0x498))

print("SYMBOL ERRORs - Lane 3")

print hex(apb_read_reg(serAddr, 0x49C))

if DES == "Ux984" or DES == "HH984":

if DPTX:

print "----------------------------------"

print "DPTX Status"

## AUX DP/eDP Train Status Read 0x202 and 0x203

board.WriteI2C(desAlias0, 0x40, 0x2D)

board.WriteI2C(desAlias0, 0x41, 0x93)

print "Page11 reg 0x93 = ", hex(board.ReadI2C(desAlias0, 0x42, 1))

for dpcdAddr in range(0x202, 0x204):

apb_write_reg(desAlias0, 0x13C, 0x1) # Clear AUX_Reply Count

# Aux read transaction to read DPCD registers

apb_write_reg(desAlias0, 0x108, dpcdAddr) # aux address

apb_write_reg(desAlias0, 0x100, 0x900) # aux Command to read

time.sleep(0.25)

AUX_REPLY_COUNT = apb_read_reg(desAlias0, 0x13C)

# print "AUX Reply Count:", AUX_REPLY_COUNT

if AUX_REPLY_COUNT == 1:

replyData = apb_read_reg(desAlias0, 0x134) # Read reply data

print "DPCD addr " + hex(dpcdAddr) + " is " + hex(replyData)

else:

print "No AUX Reply Detected"

apb_write_reg(desAlias0, 0x108, 0x202) # aux address

apb_write_reg(desAlias0, 0x100, 0x900) # aux Command to read

time.sleep(0.25)

replyData = apb_read_reg(desAlias0, 0x134) # Read reply data

apb_write_reg(desAlias0, 0x108, 0x202) # aux address

apb_write_reg(desAlias0, 0x100, 0x900) # aux Command to read

time.sleep(0.25)

replyData = apb_read_reg(desAlias0, 0x134) # Read reply data

print "'DPCD addr " + hex(0x202) + " is " + hex(replyData)

apb_write_reg(desAlias0, 0x108, 0x203) # aux address

apb_write_reg(desAlias0, 0x100, 0x900) # aux Command to read

time.sleep(0.25)

replyData = apb_read_reg(desAlias0, 0x134) # Read reply data

apb_write_reg(desAlias0, 0x108, 0x203) # aux address

apb_write_reg(desAlias0, 0x100, 0x900) # aux Command to read

time.sleep(0.25)

replyData = apb_read_reg(desAlias0, 0x134) # Read reply data

print "'DPCD addr " + hex(0x203) + " is " + hex(replyData)

for dpcdAddr in range(0x100, 0x101):

# Aux read transaction to read DPCD registers

apb_write_reg(desAlias0, 0x108, dpcdAddr) # aux address

apb_write_reg(desAlias0, 0x100, 0x900) # aux Command to read

time.sleep(0.25)

replyData = apb_read_reg(desAlias0, 0x134) # Read reply data

print "DPCD addr " + hex(dpcdAddr) + " is " + hex(replyData)

if replyData == 10:

print "DPTX = 2.7 Gbps"

if replyData == 6:

print "DPTX = 1.62 Gbps"

if replyData == 20:

print "DPTX = 5.4 Gbps"

if replyData == 30:

print "DPTX = 8.1 Gbps"

for dpcdAddr in range(0x101, 0x102):

# Aux read transaction to read DPCD registers

apb_write_reg(desAlias0, 0x108, dpcdAddr) # aux address

apb_write_reg(desAlias0, 0x100, 0x900) # aux Command to read

time.sleep(0.25)

replyData = apb_read_reg(desAlias0, 0x134) # Read reply data

print "DPCD addr " + hex(dpcdAddr) + " is " + hex(replyData)

if replyData == 0x84:

print "DP_Lanes = 4"

print "----------------------------------"

print "Des FIFO = ", hex(apb_read_reg(desAlias0, 0x1CC))

if DTGs:

print "----------------------------------"

print "DTG Port 0 Timing:"

measure = [0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0]

board.WriteI2C(desAlias0, 0x40, 0x53)

board.WriteI2C(desAlias0, 0x41, 0x40)

for x in range(0, 16, 1):

measure[x] = board.ReadI2C(desAlias0, 0x42, 1)

Htotal = (measure[0] << 8) | measure[1]

print "Htotal = ", Htotal

Vtotal = (measure[2] << 8) | measure[3]

print "Vtotal = ", Vtotal

Hactive = (measure[4] << 8) | measure[5]

print "Hactive = ", Hactive

Vactive = (measure[6] << 8) | measure[7]

print "Vactive = ", Vactive

Hstart = (measure[8] << 8) | measure[9]

print "Hstart = ", Hstart

Vstart = (measure[10] << 8) | measure[11]

Hsync = (measure[12] << 8) | measure[13]

print "Hsync = ", Hsync

Vsync = (measure[14] << 8) | measure[15]

print "Vsync = ", Vsync

Vback = Vstart - Vsync

print "Vback = ", Vback

Vfront = Vtotal - Vactive - Vsync - Vback

print "Vfront = ", Vfront

if DP0 and DES == "Ux984":

print "----------------------------------"

print "Print Des MSAs"

Measure_Video_DPTX(desAlias0, 0, 1)

print "----------------------------------"

print "Ux984 DPTX APBs"

Ux984_APB_Dump(0,desAlias0)

if DP0 and DES == "HH984":

print "----------------------------------"

print "Print Des MSAs"

Measure_Video_DPTX_HH(desAlias0, 0, 1)

if DP1 and DES == "Ux984":

print "----------------------------------"

print "Print Des MSAs"

Measure_Video_DPTX(desAlias0, 1, 1)

if DP1 and DES == "HH984":

print "----------------------------------"

print "Print Des MSAs"

Measure_Video_DPTX_HH(desAlias0, 1, 1)

if DES == "Ux988" :

print "----------------------------------"

print "Ux988 Status"

print "DES_Addr = ", hex(board.ReadI2C(desAlias0, 0x0))

for x in range(10):

# print ("Link and Lock Status")

print "Ser Reg 0xC = ", hex(board.ReadI2C(serAddr, 0xC, 1)), ",",

print "Des Reg 0x53 = ", hex(board.ReadI2C(desAlias0, 0x53, 1)), ",",

print "Des Reg 0x54 = ", hex(board.ReadI2C(desAlias0, 0x54, 1)), ",",

board.WriteI2C(serAddr, 0x40, 18 * 4 + 1)

board.WriteI2C(serAddr, 0x41, 0x4E)

print "Des Reg 0x4E = ", hex(board.ReadI2C(desAlias0, 0x42))

measure = [0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0]

board.WriteI2C(desAlias0, 0x40, 0x53)

board.WriteI2C(desAlias0, 0x41, 0x40)

for x in range(0, 16, 1):

measure[x] = board.ReadI2C(desAlias0, 0x42, 1)

print "----------------------------------"

print "Ux988 DTGs"

Htotal = (measure[0] << 8) | measure[1]

print "Htotal = ", Htotal

Vtotal = (measure[2] << 8) | measure[3]

print "Vtotal = ", Vtotal

Hactive = (measure[4] << 8) | measure[5]

print "Hactive = ", Hactive

Vactive = (measure[6] << 8) | measure[7]

print "Vactive = ", Vactive

Hstart = (measure[8] << 8) | measure[9]

print "Hstart = ", Hstart

Vstart = (measure[10] << 8) | measure[11]

Hsync = (measure[12] << 8) | measure[13]

print "Hsync = ", Hsync

Vsync = (measure[14] << 8) | measure[15]

print "Vsync = ", Vsync

Vback = Vstart - Vsync

print "Vback = ", Vback

Vfront = Vtotal - Vactive - Vsync - Vback

print "Vfront = ", Vfront

board.WriteI2C(desAlias0, 0x41, 0x70)

board.WriteI2C(desAlias0, 0x41, 0xA0)

print "FPD IV Link Layer Timing:"

board.WriteI2C(desAlias0, 0x40, 0x4B)

board.WriteI2C(desAlias0, 0x41, 0x39)

for x in range(0, 12, 1):

measure[x] = board.ReadI2C(desAlias0, 0x42)

Stream0 = (measure[1] << 8) | measure[0]

Stream1 = (measure[3] << 8) | measure[2]

Stream2 = (measure[5] << 8) | measure[4]

Stream3 = (measure[7] << 8) | measure[6]

Stream4 = (measure[9] << 8) | measure[8]

Stream5 = (measure[11] << 8) | measure[10]

print "Stream 0 Hactive = ", Stream0

print "Stream 1 Hactive = ", Stream1

print "Stream 2 Hactive = ", Stream2

print "Stream 3 Hactive = ", Stream3

print "Stream 4 Hactive = ", Stream4

print "Stream 5 Hactive = ", Stream5

if SER == "Ux983":

print "-------------------------"

print "Ux983_APB_dump"

Ux983_APBs(0)

if SER == "HH983":

print "-------------------------"

print "HH983_APB_dump"

HH983_APBs()

Ux98x_SERDES_Full_Diagnostics()

time.sleep(0.1)

## TI Confidential - NDA Restrictions

##

## Copyright 2018 Texas Instruments Incorporated. All rights reserved.

##

## IMPORTANT: Your use of this Software is limited to those specific rights

## granted under the terms of a software license agreement between the user who

## downloaded the software, his/her employer (which must be your employer) and

## Texas Instruments Incorporated (the License). You may not use this Software

## unless you agree to abide by the terms of the License. The License limits your

## use, and you acknowledge, that the Software may not be modified, copied or

## distributed unless embedded on a Texas Instruments microcontroller which is

## integrated into your product. Other than for the foregoing purpose, you may

## not use, reproduce, copy, prepare derivative works of, modify, distribute,

## perform, display or sell this Software and/or its documentation for any

## purpose.

##

## YOU FURTHER ACKNOWLEDGE AND AGREE THAT THE SOFTWARE AND DOCUMENTATION ARE

## PROVIDED AS IS WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED,

## INCLUDING WITHOUT LIMITATION, ANY WARRANTY OF MERCHANTABILITY, TITLE,

## NON-INFRINGEMENT AND FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL TEXAS

## INSTRUMENTS OR ITS LICENSORS BE LIABLE OR OBLIGATED UNDER CONTRACT,

## NEGLIGENCE, STRICT LIABILITY, CONTRIBUTION, BREACH OF WARRANTY, OR OTHER LEGAL

## EQUITABLE THEORY ANY DIRECT OR INDIRECT DAMAGES OR EXPENSES INCLUDING BUT NOT

## LIMITED TO ANY INCIDENTAL, SPECIAL, INDIRECT, PUNITIVE OR CONSEQUENTIAL

## DAMAGES, LOST PROFITS OR LOST DATA, COST OF PROCUREMENT OF SUBSTITUTE GOODS,

## TECHNOLOGY, SERVICES, OR ANY CLAIMS BY THIRD PARTIES (INCLUDING BUT NOT

## LIMITED TO ANY DEFENSE THEREOF), OR OTHER SIMILAR COSTS.

##

## Should you have any questions regarding your right to use this Software,

## contact Texas Instruments Incorporated at www.TI.com.

## Debug Script Version 1

import time

#######################User_Input############################

serAddr = 0x18

desAlias0 = 0x58

SER = "Ux983" # Chosse HH983 or Ux983 or Ux943A or Ux981 or Ux94x

DES = "Ux984" # Chosse HH984 or Ux984 or Ux988 or Ux948

MST = 0 # For Ux983 Select 0 for SST and 1 for MST mode

DP0 = 1 # For Ux984 Enable DPTX port0 diagnostics

DP1 = 0 # For Ux984 Enable DPTX port1 diagnostics

##################Keep Always ON#############################

VP = 1 # Enable VP diagnostics

SER_MSAs = 1 # Dump 983 SER MSAs

DTGs = 1 # dump DES DTGs

DPRX = 1 # Enable 983 DPRX diagnostics

DPTX = 1 # Enable 984 DPTX diagnostics

#############################################################

def apb_read_reg(DevAddrRxMain, addr16b):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

board.WriteI2C(DevAddrRxMain, APB_ADR0, addr16b_lsb)

board.WriteI2C(DevAddrRxMain, APB_ADR1, addr16b_msb)

board.WriteI2C(DevAddrRxMain, APB_CTL, 0x03)

apbData0 = board.ReadI2C(DevAddrRxMain, APB_DATA0)

apbData1 = board.ReadI2C(DevAddrRxMain, APB_DATA1)

apbData2 = board.ReadI2C(DevAddrRxMain, APB_DATA2)

apbData3 = board.ReadI2C(DevAddrRxMain, APB_DATA3)

apbData = (apbData3 << 24) | (apbData2 << 16) | (apbData1 << 8) | (apbData0 << 0)

val32bit = apbData

return val32bit

def apb_write_reg(DevAddrRxMain, addr16b, data32b):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

board.WriteI2C(DevAddrRxMain, APB_ADR0, addr16b_lsb)

board.WriteI2C(DevAddrRxMain, APB_ADR1, addr16b_msb)

# print 'data32b', data32b

apbData0 = int((data32b & 0x000000FF) >> 0)

# print 'type', type(apbData0), apbData0

apbData1 = int((data32b & 0x0000FF00) >> 8)

apbData2 = int((data32b & 0x00FF0000) >> 16)

apbData3 = int((data32b & 0xFF000000) >> 24)

board.WriteI2C(DevAddrRxMain, APB_DATA0, apbData0)

board.WriteI2C(DevAddrRxMain, APB_DATA1, apbData1)

board.WriteI2C(DevAddrRxMain, APB_DATA2, apbData2)

board.WriteI2C(DevAddrRxMain, APB_DATA3, apbData3)

board.WriteI2C(DevAddrRxMain, APB_CTL, 0x01)

def MSA_apb_read_reg(addr16b, channel, Device_ID):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

if channel == 0:

page = 0x03

elif channel == 1:

page = 0x0B

else:

page = 0x03

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

board.WriteI2C(Device_ID, APB_ADR0, addr16b_lsb)

board.WriteI2C(Device_ID, APB_ADR1, addr16b_msb)

board.WriteI2C(Device_ID, APB_CTL, page)

apbData0 = board.ReadI2C(Device_ID, APB_DATA0)

apbData1 = board.ReadI2C(Device_ID, APB_DATA1)

apbData2 = board.ReadI2C(Device_ID, APB_DATA2)

apbData3 = board.ReadI2C(Device_ID, APB_DATA3)

apbData = (apbData3 << 24) + (apbData2 << 16) + (apbData1 << 8) + (apbData0 << 0)

val32bit = apbData

return val32bit

def Measure_Video_DPTX(desAlias0, Port, PRNT_STATUS):

print("")

Offset = 0x00

htotal = MSA_apb_read_reg(0x180 + Offset, int(Port), desAlias0)

vtotal = MSA_apb_read_reg(0x184 + Offset, int(Port), desAlias0)

hres = MSA_apb_read_reg(0x194 + Offset, int(Port), desAlias0)

vres = MSA_apb_read_reg(0x198 + Offset, int(Port), desAlias0)

hstart = MSA_apb_read_reg(0x19C + Offset, int(Port), desAlias0)

vstart = MSA_apb_read_reg(0x1A0 + Offset, int(Port), desAlias0)

hswidth = MSA_apb_read_reg(0x18C + Offset, int(Port), desAlias0)

vswidth = MSA_apb_read_reg(0x190 + Offset, int(Port), desAlias0)

if PRNT_STATUS == 1:

print("Port", Port, ": DPTX VIDEO RESOLUTION:")

print("Port", Port, ": htotal (0x180) = " + str(htotal))

print("Port", Port, ": vtotal (0x184) = " + str(vtotal))

print("Port", Port, ": hres (0x18C) = " + str(hres))

print("Port", Port, ": vres (0x190) = " + str(vres))

print("Port", Port, ": hstart (0x19C) = " + str(hstart))

print("Port", Port, ": vstart (0x1A0) = " + str(vstart))

print("Port", Port, ": hswidth (0x18C) = " + str(hswidth))

print("Port", Port, ": vswidth (0x18C) = " + str(vswidth))

return htotal, hres, vtotal, vres

def Measure_Video_DPTX_HH(desAlias0, Port, PRNT_STATUS):

print("")

Offset = 0x00

htotal = MSA_apb_read_reg(0x820 + Offset, int(Port), desAlias0)

vtotal = MSA_apb_read_reg(0x824 + Offset, int(Port), desAlias0)

hres = MSA_apb_read_reg(0x834 + Offset, int(Port), desAlias0)

vres = MSA_apb_read_reg(0x838 + Offset, int(Port), desAlias0)

hstart = MSA_apb_read_reg(0x83C + Offset, int(Port), desAlias0)

vstart = MSA_apb_read_reg(0x840 + Offset, int(Port), desAlias0)

hswidth = MSA_apb_read_reg(0x82C + Offset, int(Port), desAlias0)

vswidth = MSA_apb_read_reg(0x830 + Offset, int(Port), desAlias0)

if PRNT_STATUS == 1:

print("Port", Port, ": DPTX VIDEO RESOLUTION:")

print("Port", Port, ": htotal (0x820) = " + str(htotal))

print("Port", Port, ": vtotal (0x824) = " + str(vtotal))

print("Port", Port, ": hres (0x834) = " + str(hres))

print("Port", Port, ": vres (0x838) = " + str(vres))

print("Port", Port, ": hstart (0x83C) = " + str(hstart))

print("Port", Port, ": vstart (0x840) = " + str(vstart))

print("Port", Port, ": hswidth (0x82C) = " + str(hswidth))

print("Port", Port, ": vswidth (0x830) = " + str(vswidth))

return htotal, hres, vtotal, vres

def apb_read_reg_984_DPTX(addr16b, channel, Device_ID):

APB_CTL = 0x48

APB_AUTO_INC = {'pos': 2, 'wid': 1}

APB_READ = {'pos': 1, 'wid': 1}

APB_ENABLE = {'pos': 0, 'wid': 1}

APB_ADR0 = 0x49

APB_ADR1 = 0x4A

APB_DATA0 = 0x4B

APB_DATA1 = 0x4C

APB_DATA2 = 0x4D

APB_DATA3 = 0x4E

if channel == 0:

page = 0x03

elif channel == 1:

page = 0x0B

else:

page = 0x03

addr16b_lsb = addr16b & 0xFF

addr16b_msb = (addr16b & 0xFF00) >> 8

##print 'READ inst'

board.WriteI2C(Device_ID, APB_ADR0, addr16b_lsb)

board.WriteI2C(Device_ID, APB_ADR1, addr16b_msb)

board.WriteI2C(Device_ID, APB_CTL, page)

apbData0 = board.ReadI2C(Device_ID, APB_DATA0)

apbData1 = board.ReadI2C(Device_ID, APB_DATA1)

apbData2 = board.ReadI2C(Device_ID, APB_DATA2)

apbData3 = board.ReadI2C(Device_ID, APB_DATA3)

apbData = (apbData3 << 24) + (apbData2 << 16) + (apbData1 << 8) + (apbData0 << 0)

val32bit = apbData

Device_ID = 0x00

return val32bit

def Ux984_APB_Dump(Port,Device_RX):

Stream = 0 # 0, 1, 2, or 3

if Stream == 0 :

Offset = 0x00

elif Stream == 1:

Offset = 0x400

elif Stream == 2:

Offset = 0x420

elif Stream == 3:

Offset = 0x500

else:

Offset = 0x00

print "PORT ",Port," DPTX APB Dump: Main Stream Attributes"

REG_000= apb_read_reg_984_DPTX(0x000,int(Port), Device_RX )

print "REG_000 (LINK_BW_SET) = ", (REG_000)

REG_004= apb_read_reg_984_DPTX(0x004,int(Port), Device_RX )

print "REG_004 (LANE_COUNT_SET) = ", (REG_004)

REG_008= apb_read_reg_984_DPTX(0x008,int(Port), Device_RX )

print "REG_008 (ENHANCED_FRAME_EN) = ", (REG_008)

REG_00C= apb_read_reg_984_DPTX(0x00C,int(Port), Device_RX )

print "REG_00C (TRAINING_PATTERN_SET) = ", (REG_00C)

REG_010= apb_read_reg_984_DPTX(0x010,int(Port), Device_RX )

print "REG_010 (LINK_QUAL_PATTERN_SET) = ", (REG_010)

REG_014= apb_read_reg_984_DPTX(0x014,int(Port), Device_RX )

print "REG_014 (SCRAMBLING_DISABLE) = ", (REG_014)

REG_018= apb_read_reg_984_DPTX(0x018,int(Port), Device_RX )

print "REG_018 (DOWNSPREAD_CTRL) = ", (REG_018)

REG_01C= apb_read_reg_984_DPTX(0x01C,int(Port), Device_RX )

print "REG_01C (EDP_CAPABILITY_CONFIG) = ", (REG_01C)

REG_020= apb_read_reg_984_DPTX(0x020,int(Port), Device_RX )

print "REG_020 (HBR2_COMPLIANCE_SCRAMBLER_RESET) = ", (REG_020)

REG_024= apb_read_reg_984_DPTX(0x024,int(Port), Device_RX )

print "REG_024 (DISPLAYPORT_VERSION) = ", (REG_024)

REG_028= apb_read_reg_984_DPTX(0x028,int(Port), Device_RX )

print "REG_024 (PHY_POWER_STATE) = ", (REG_028)

REG_02C= apb_read_reg_984_DPTX(0x02C,int(Port), Device_RX )

print "REG_02C (LANE_REMAP_CONTROL) = ", (REG_02C)

REG_030= apb_read_reg_984_DPTX(0x030,int(Port), Device_RX )

print "REG_030 (CUSTOM_80BIT_PATTERN_0) = ", (REG_030)

REG_034= apb_read_reg_984_DPTX(0x034,int(Port), Device_RX )

print "REG_034 (CUSTOM_80BIT_PATTERN_1) = ", (REG_034)

REG_038= apb_read_reg_984_DPTX(0x038,int(Port), Device_RX )

print "REG_038 (CUSTOM_80BIT_PATTERN_2) = ", (REG_038)

REG_060= apb_read_reg_984_DPTX(0x060,int(Port), Device_RX )

print "REG_060 (FEC_ENABLE) = ", (REG_060)

REG_080= apb_read_reg_984_DPTX(0x080,int(Port), Device_RX )

print "REG_080 (TRANSMITTER_OUTPUT_ENABLE) = ", (REG_080)

REG_084= apb_read_reg_984_DPTX(0x084,int(Port), Device_RX )

print "REG_084 (VIDEO_STREAM_ENABLE) = ", (REG_084)

REG_088= apb_read_reg_984_DPTX(0x088,int(Port), Device_RX )

print "REG_088 (SECONDARY_STREAM_ENABLE) = ", (REG_088)

REG_08C= apb_read_reg_984_DPTX(0x08C,int(Port), Device_RX )

print "REG_088 (SECONDARY_DATA_WINDOW) = ", (REG_08C)

REG_090= apb_read_reg_984_DPTX(0x090,int(Port), Device_RX )

print "REG_090 (SOFT_RESET) = ", (REG_090)

REG_094= apb_read_reg_984_DPTX(0x094,int(Port), Device_RX )

print "REG_094 (INPUT_SOURCE_ENABLE) = ", (REG_094)

REG_098= apb_read_reg_984_DPTX(0x098,int(Port), Device_RX )

print "REG_098 (FEC_ENABLE) = ", (REG_098)

REG_0C0= apb_read_reg_984_DPTX(0x0C0,int(Port), Device_RX )

print "REG_0C0 (ORCE_SCRAMBLER_RESET) = ", (REG_0C0)

REG_0C4= apb_read_reg_984_DPTX(0x0C4,int(Port), Device_RX )

print "REG_0C4 (USER_CONTROL_STATUS) = ", (REG_0C4)

REG_0C8= apb_read_reg_984_DPTX(0x0C8,int(Port), Device_RX )

print "REG_0C8 (USER_DATA_CONTROL) = ", (REG_0C8)

REG_0F8= apb_read_reg_984_DPTX(0x0F8,int(Port), Device_RX )

print "REG_0F8 (CORE_CAPABILITIES) = ", (REG_0F8)

REG_0FC= apb_read_reg_984_DPTX(0x0FC,int(Port), Device_RX )

print "REG_0FC (CORE_ID) = ", (REG_0FC)

REG_100= apb_read_reg_984_DPTX(0x100,int(Port), Device_RX )

print "REG_100 (AUX_COMMAND) = ", (REG_100)

REG_104= apb_read_reg_984_DPTX(0x104,int(Port), Device_RX )

print "REG_104 (AUX_WRITE_FIFO) = ", (REG_104)

REG_108= apb_read_reg_984_DPTX(0x108,int(Port), Device_RX )

print "REG_108 (AUX_ADDRESS) = ", (REG_108)

REG_10C= apb_read_reg_984_DPTX(0x10C,int(Port), Device_RX )

print "REG_10C (AUX_CLOCK_DIVIDER) = ", (REG_10C)

REG_110= apb_read_reg_984_DPTX(0x110,int(Port), Device_RX )

print "REG_110 (AUX_REPLY_TIMEOUT_INTERVAL) = ", (REG_110)

REG_128= apb_read_reg_984_DPTX(0x128,int(Port), Device_RX )

print "REG_128 (SINK_HPD_STATE) = ", (REG_128)

REG_130= apb_read_reg_984_DPTX(0x130,int(Port), Device_RX )

print "REG_130 (INTERRUPT_STATE) = ", (REG_130)

REG_134= apb_read_reg_984_DPTX(0x134,int(Port), Device_RX )

print "REG_134 (AUX_REPLY_DATA) = ", (REG_134)

REG_138= apb_read_reg_984_DPTX(0x138,int(Port), Device_RX )

print "REG_138 (AUX_REPLY_CODE) = ", (REG_138)

REG_13C= apb_read_reg_984_DPTX(0x13C,int(Port), Device_RX )

print "REG_13C (AUX_REPLY_COUNT) = ", (REG_13C)

REG_140= apb_read_reg_984_DPTX(0x140,int(Port), Device_RX )

print "REG_140 (INTERRUPT_STATUS) = ", (REG_140)

REG_144= apb_read_reg_984_DPTX(0x144,int(Port), Device_RX )

print "REG_144 (INTERRUPT_MASK) = ", (REG_144)

REG_148= apb_read_reg_984_DPTX(0x148,int(Port), Device_RX )

print "REG_148 (REPLY_DATA_COUNT) = ", (REG_148)

REG_14C= apb_read_reg_984_DPTX(0x14C,int(Port), Device_RX )

print "REG_14C (AUX_STATUS) = ", (REG_14C)

REG_150= apb_read_reg_984_DPTX(0x150,int(Port), Device_RX )

print "REG_150 (AUX_REPLY_CLOCK_WIDTH) = ", (REG_150)

REG_154= apb_read_reg_984_DPTX(0x154,int(Port), Device_RX )

print "REG_154 (AUX_WAKE_ACK_DETECTED) = ", (REG_154)

REG_158= apb_read_reg_984_DPTX(0x158,int(Port), Device_RX )

print "REG_158 (GP_HOST_TIMER) = ", (REG_158)

print ""

print "STREAM: ", Stream, " Register Read: "

print ""

REG_0180= apb_read_reg_984_DPTX(0x180+Offset,int(Port), Device_RX )

print "REG_0180 (MAIN_STREAM_HTOTAL) = ", (REG_0180)

REG_0184= apb_read_reg_984_DPTX(0x184+Offset,int(Port), Device_RX )

print "REG_0184 (MAIN_STREAM_VTOTAL) = ", (REG_0184)

REG_0188= apb_read_reg_984_DPTX(0x188+Offset,int(Port), Device_RX )

print "REG_0188 (MAIN_STREAM_POLARITY) = ", (REG_0188)

REG_018C= apb_read_reg_984_DPTX(0x18C+Offset,int(Port), Device_RX )

print "REG_018C (MAIN_STREAM_HSWIDTH) = ", (REG_018C)

REG_0190= apb_read_reg_984_DPTX(0x190+Offset,int(Port), Device_RX )

print "REG_0190 (MAIN_STREAM_VSWIDTH) = ", (REG_0190)

REG_0194= apb_read_reg_984_DPTX(0x194+Offset,int(Port), Device_RX )

print "REG_0194 (MAIN_STREAM_HRES) = ", (REG_0194)

REG_0198= apb_read_reg_984_DPTX(0x198+Offset,int(Port), Device_RX )

print "REG_0198 (MAIN_STREAM_VRES) = ", (REG_0198)

REG_019C= apb_read_reg_984_DPTX(0x19C+Offset,int(Port), Device_RX )

print "REG_019C (MAIN_STREAM_HSTART) = ", (REG_019C)

REG_01A0= apb_read_reg_984_DPTX(0x1A0+Offset,int(Port), Device_RX )

print "REG_01A0 (MAIN_STREAM_VSTART) = ", (REG_01A0)

REG_01A4= apb_read_reg_984_DPTX(0x1A4+Offset,int(Port), Device_RX )

print "REG_01A4 (MAIN_STREAM_MISC0) = ", (REG_01A4)

REG_01A8= apb_read_reg_984_DPTX(0x1A8+Offset,int(Port), Device_RX )

print "REG_01A8 (MAIN_STREAM_MISC1) = ", (REG_01A8)

REG_01AC= apb_read_reg_984_DPTX(0x1AC+Offset,int(Port), Device_RX )

print "REG_01AC (MVID) = ", (REG_01AC)

REG_01B0= apb_read_reg_984_DPTX(0x1B0+Offset,int(Port), Device_RX )

print "REG_01B0 (TRANSFER_UNIT_CONFIG_SRC_0) = ", (REG_01B0)

REG_01B4= apb_read_reg_984_DPTX(0x1B4+Offset,int(Port), Device_RX )

print "REG_01B4 (NVID) = ", (REG_01B4)

REG_01B8= apb_read_reg_984_DPTX(0x1B8+Offset,int(Port), Device_RX )

print "REG_01B8 (USER_PIXEL_COUNT) = ", (REG_01B8)

REG_01BC= apb_read_reg_984_DPTX(0x1BC+Offset,int(Port), Device_RX )

print "REG_01BC (USER_DATA_COUNT) = ", (REG_01BC)

REG_01C0= apb_read_reg_984_DPTX(0x1C0+Offset,int(Port), Device_RX )

print "REG_01C0 (MAIN_STREAM_INTERLACED) = ", (REG_01C0)

REG_01C4= apb_read_reg_984_DPTX(0x1C4+Offset,int(Port), Device_RX )

print "REG_01C4 (USER_SYNC_POLARITY) = ", (REG_01C4)

REG_01C8= apb_read_reg_984_DPTX(0x1C8+Offset,int(Port), Device_RX )

print "REG_01C8 (USER_CONTROL) = ", (REG_01C8)

REG_01CC= apb_read_reg_984_DPTX(0x1CC+Offset,int(Port), Device_RX )

print "REG_01CC (USER_CONTROL) = ", (REG_01CC)

REG_0500= apb_read_reg_984_DPTX(0x500,int(Port), Device_RX )

print "REG_0500 (MST_ENABLE) = ", (REG_0500)

REG_0504= apb_read_reg_984_DPTX(0x504,int(Port), Device_RX )

print "REG_0504 (MST_PID_TABLE_INDEX) = ", (REG_0504)

REG_0508= apb_read_reg_984_DPTX(0x504,int(Port), Device_RX )

print "REG_0508 (MST_PID_TABLE_ENTRY) = ", (REG_0508)

REG_050C= apb_read_reg_984_DPTX(0x50C,int(Port), Device_RX )

print "REG_050C (SST_SOURCE_SELECT) = ", (REG_050C)

REG_0510= apb_read_reg_984_DPTX(0x510,int(Port), Device_RX )

print "REG_0510 (MST_ALLOCATION_TRIGGER) = ", (REG_0510)

REG_0514= apb_read_reg_984_DPTX(0x514,int(Port), Device_RX )

print "REG_0514 (MST_PID_TABLE_SELECT) = ", (REG_0514)

REG_0518= apb_read_reg_984_DPTX(0x518,int(Port), Device_RX )

print "REG_0518 (MST_ACTIVE_PAYLOAD_TABLE) = ", (REG_0518)

REG_0520= apb_read_reg_984_DPTX(0x520,int(Port), Device_RX )

print "REG_0520 (MST_ACTIVE) = ", (REG_0520)

REG_0524= apb_read_reg_984_DPTX(0x524,int(Port), Device_RX )

print "REG_0524 (MST_LINK_FRAME_COUNT) = ", (REG_0524)

REG_0528= apb_read_reg_984_DPTX(0x528,int(Port), Device_RX )

print "REG_0528 (MSO_CONFIGURATION) = ", (REG_0528)

REG_0528= apb_read_reg_984_DPTX(0x528,int(Port), Device_RX )

print "REG_0528 (MSO_CONFIGURATION) = ", (REG_0528)

# Port = 1

# print ""

# print "PORT ",Port," DPTX APB Dump: Main Stream Attributes"

# print ""

# REG_000= apb_read_reg(0x000,int(Port), Device_RX )

# print "REG_000 (LINK_BW_SET) = ", (REG_000)

# REG_004= apb_read_reg(0x004,int(Port), Device_RX )

# print "REG_004 (LANE_COUNT_SET) = ", (REG_004)

# REG_008= apb_read_reg(0x008,int(Port), Device_RX )

# print "REG_008 (ENHANCED_FRAME_EN) = ", (REG_008)

# REG_00C= apb_read_reg(0x00C,int(Port), Device_RX )

# print "REG_00C (TRAINING_PATTERN_SET) = ", (REG_00C)

# REG_010= apb_read_reg(0x010,int(Port), Device_RX )

# print "REG_010 (LINK_QUAL_PATTERN_SET) = ", (REG_010)

# REG_014= apb_read_reg(0x014,int(Port), Device_RX )

# print "REG_014 (SCRAMBLING_DISABLE) = ", (REG_014)

# REG_018= apb_read_reg(0x018,int(Port), Device_RX )

# print "REG_018 (DOWNSPREAD_CTRL) = ", (REG_018)

# REG_01C= apb_read_reg(0x01C,int(Port), Device_RX )

# print "REG_01C (EDP_CAPABILITY_CONFIG) = ", (REG_01C)

# REG_020= apb_read_reg(0x020,int(Port), Device_RX )

# print "REG_020 (HBR2_COMPLIANCE_SCRAMBLER_RESET) = ", (REG_020)

# REG_024= apb_read_reg(0x024,int(Port), Device_RX )

# print "REG_024 (DISPLAYPORT_VERSION) = ", (REG_024)

# REG_028= apb_read_reg(0x028,int(Port), Device_RX )

# print "REG_024 (PHY_POWER_STATE) = ", (REG_028)

# REG_02C= apb_read_reg(0x02C,int(Port), Device_RX )

# print "REG_02C (LANE_REMAP_CONTROL) = ", (REG_02C)

# REG_030= apb_read_reg(0x030,int(Port), Device_RX )

# print "REG_030 (CUSTOM_80BIT_PATTERN_0) = ", (REG_030)

# REG_034= apb_read_reg(0x034,int(Port), Device_RX )

# print "REG_034 (CUSTOM_80BIT_PATTERN_1) = ", (REG_034)

# REG_038= apb_read_reg(0x038,int(Port), Device_RX )

# print "REG_038 (CUSTOM_80BIT_PATTERN_2) = ", (REG_038)