Part Number: DP83822HF

使用STM32H735+DP83822HF,基于LwIP实现UDP通信,将PHY作为RMII Master模式。希望能帮忙分析是硬件有故障还是软件存在bug。

- 硬件电路设计中,PHY的引脚26(RX_DV)悬空,导致上电默认strap为MII模式,因此选择软件修改寄存器并数字重启,以强制为RMII Master模式。但是GPIO3监测不到任何时钟信号输出。具体操作如下:

(1)针对0x0017:/* 强制配置为 RMII Master 模式 */reg_val &= ~(1 << 9); // 清除 RGMII 使能位(bit9),防止冲突reg_val |= (1 << 5); // 置位 RMII 使能位(bit5)reg_val &= ~(1 << 7); // 时钟选择25M:0 = 25MHzRMII Master,1 = 50MHzRMII Slave(2)针对0x001F:修改bit14 = 1,启动数字重启并等待重启完成。

- 过程中发现:插上网线ETH才有概率初始化成功。不插网线则ETH无法初始化成功。软件实现流程为(1)硬件重启PHY;(2)配置ETH并初始化;(3)PHY初始化、强制RMIIMaster并数字重启;(4)检查链路状态...

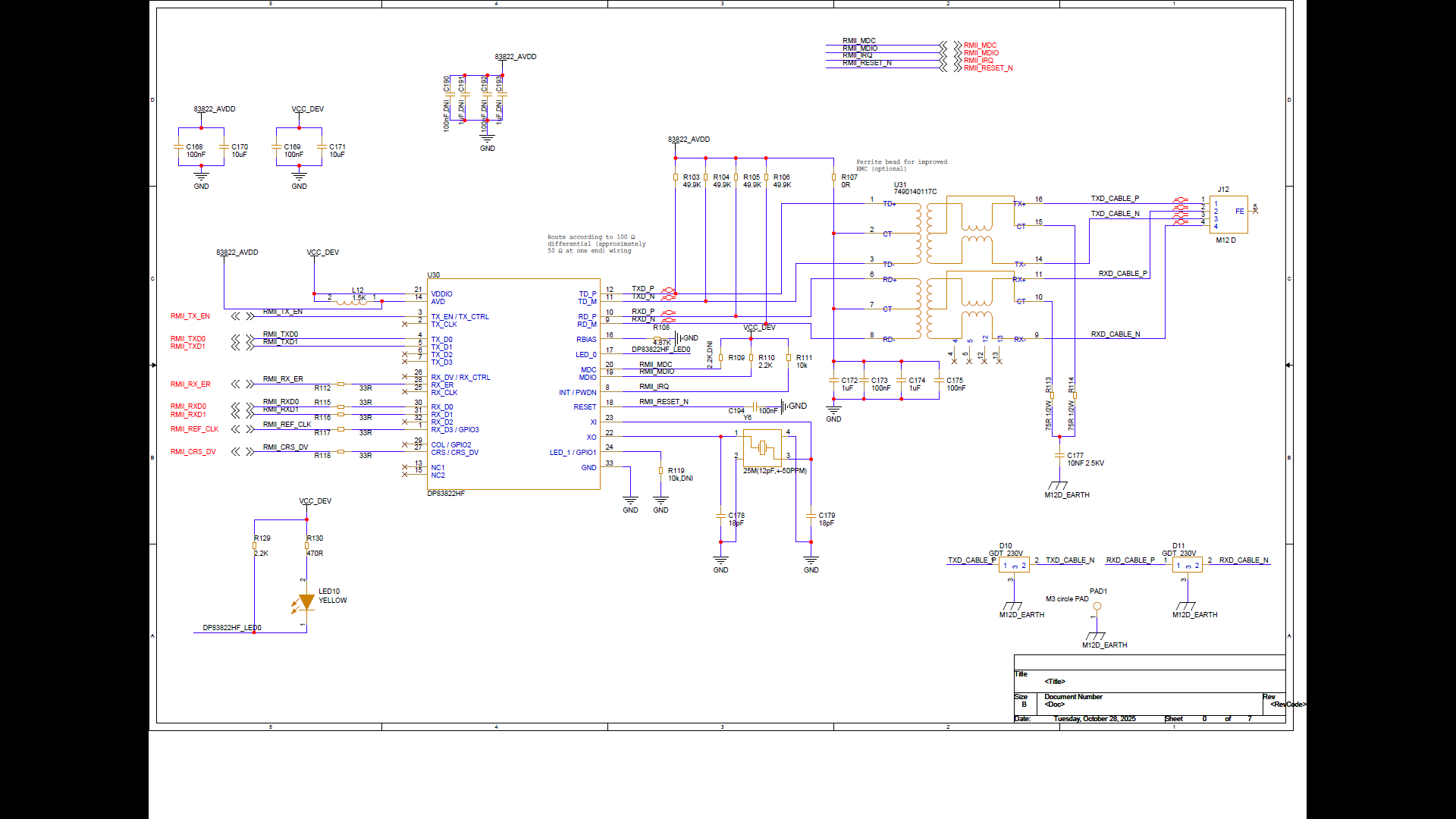

- 硬件电路如图所示: