Part Number: DS90UB941AS-Q1

Other Parts Discussed in Thread: DS90UB928Q-Q1

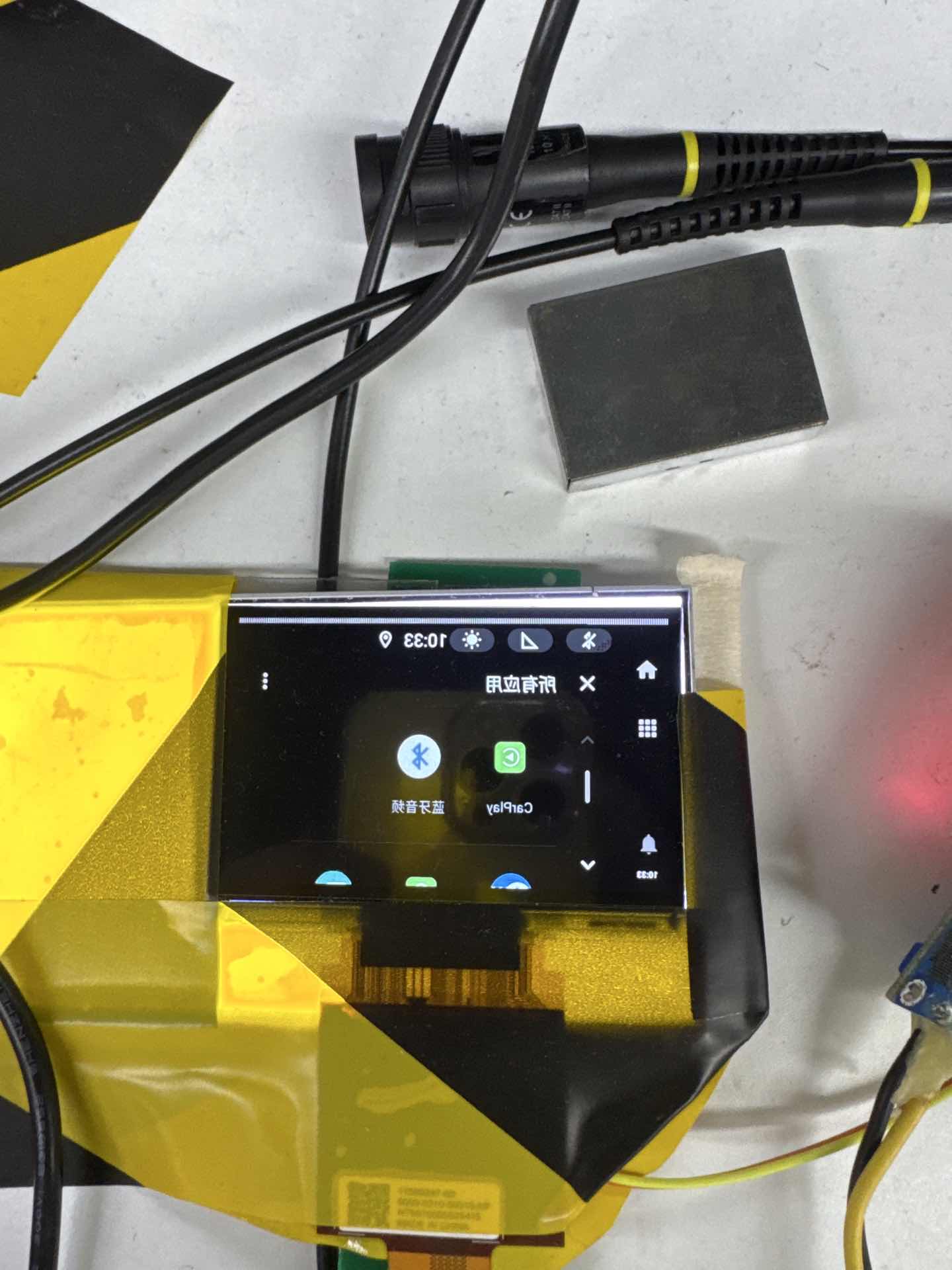

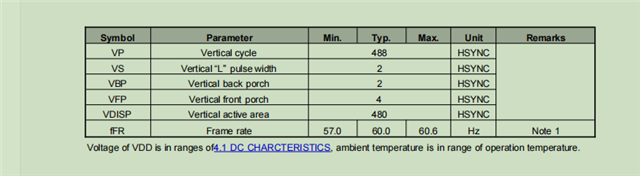

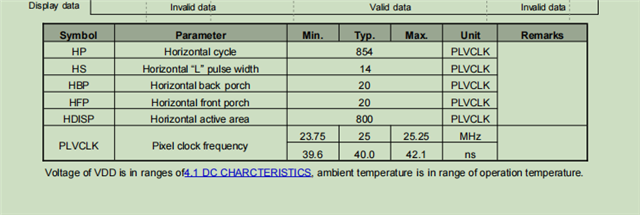

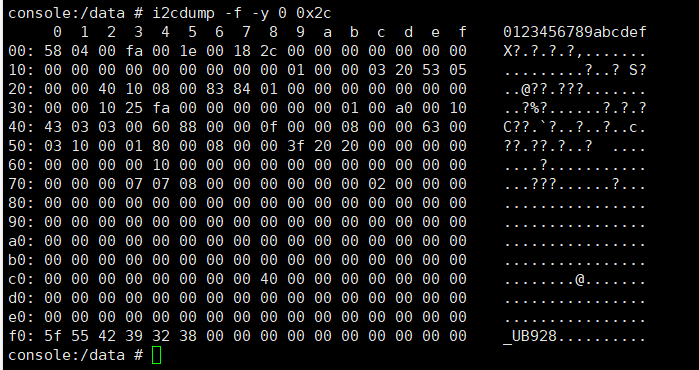

We have a project using the ds90ub941as-q1 and ds90ub928q-q1 chips. Despite repeated debugging of screen parameters on the SoC side, the image cannot be shifted upward to fully cover the entire screen (as shown in the attached document). Is there a debugging solution related to the Serializer/Deserializer (SerDes) registers to address this issue?