Other Parts Discussed in Thread: SN65DSI86

Hi TI team,

在使用贵司SNx5DPHY440SS时遇到了一些问题,需要寻求一个技术支持,问题描述如下:

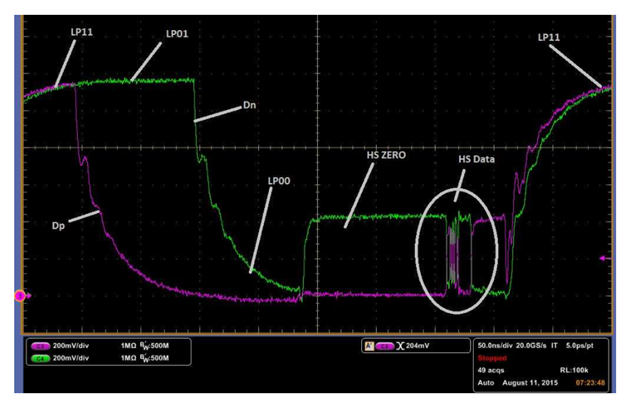

我们sensor mipi使用的是continue mode,经过这颗mipi re-timer ic后,各个通道mipi都有输出,但是平台端接收mipi信号异常;进行了一些测试及排查,具体情况说明:

1、在该ic只上电但不进行任何配置的情况下,使用其他non-continue mode的sensor经过该ic,平台端(度信)接收mipi正常;

2、在该ic只上电但不进行任何配置的情况下,使用该continue mode的sensor经过该ic,平台端(度信)接收mipi异常,无法接收到mipi数据;

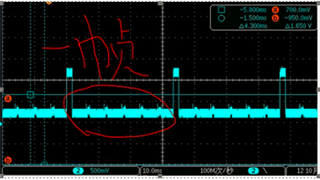

3、在该ic只上电但不进行任何配置的情况下,测量输入输出mipi波形,发现clk lane有一些异常:

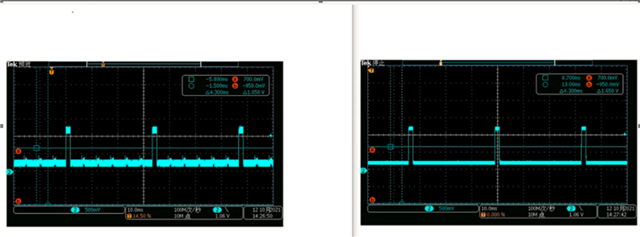

输入该ic(左) vs 输出该ic(右)

需要说明一下,该sensor在帧间会对mipi进行复位动作,因此在帧间电平会拉高,下面的红圈是一帧数据,为continue mode,但是整体看上去比较奇怪

图中明显看到经过ic后输出的mipi波形hs阶段的电平波形不正常;

4、在该ic只上电但不进行任何配置的情况下,飞线跳过该mipi re-timer ic,平台端接收正常;

5、供应商fae提供了一组用于continue mode的配置:

(0x50, 0x10),

(0x51, 0x10),

(0x61, 0x0f),

(0x70, 0x10),

(0x71,0x10),

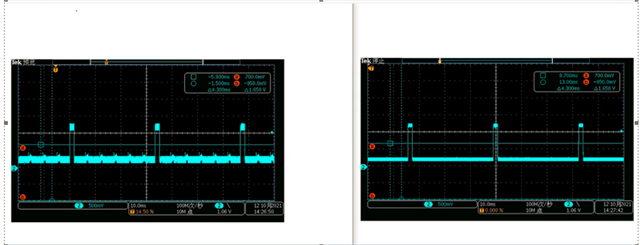

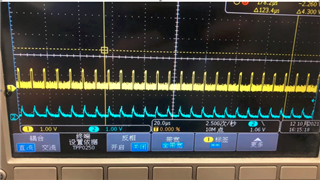

对ic写入这组配置后,data lane明显发生异常,平台端无法接收数据:

黄色为输入 蓝色为输出

6、把0x50,0x51去掉,写入配置:

//(0x50, 0x10),

// (0x51, 0x10),

(0x61, 0x0f),

(0x70, 0x10),

(0x71,0x10),

data lane输出正常,平台端接收依旧异常,但是偶尔能接到1、2帧(sensor30帧输出,最终平台帧率在1-2帧左右)

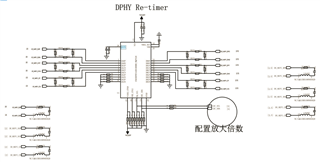

7、硬件连接:

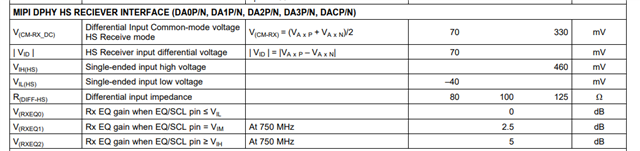

8、目前我们的mipi速率为1.4Gps。

情况如上面所说,我们这边希望拿到一组推荐寄存器配置,可以使经过该ic以后的信号可以被平台正常接收。谢谢!