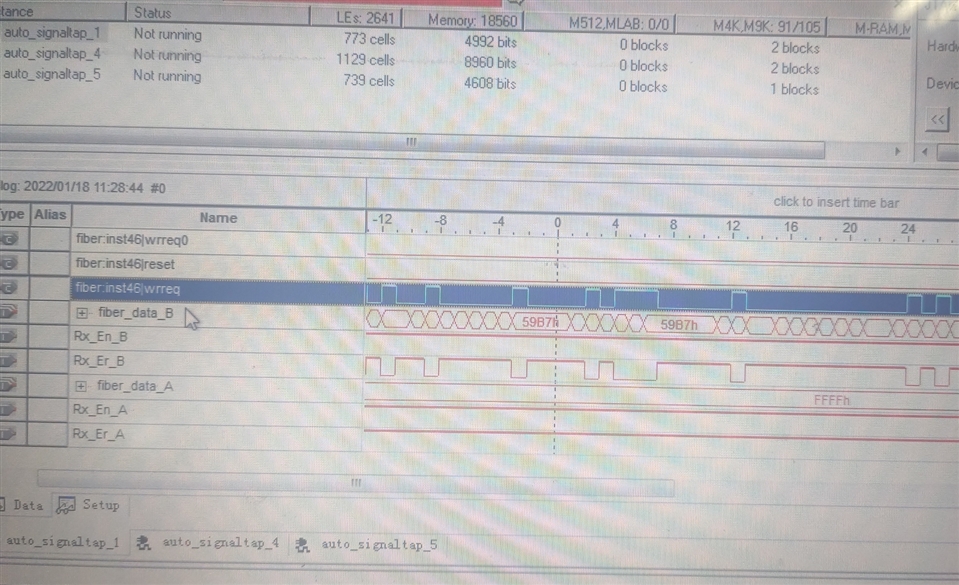

问题,两块板子2501收发测试,接收侧rx er经常拉高,数据也不对。

- 具体,接收端和发送段都是使用FPGA+2501结构。两个板子各自做光纤外部环回不会拉高rxer。发送段gtx clk为60m,enable信号只是在要发送前才开始拉高。接收侧gtxclk源不一样,大小也是60m,enable信号永远为1。发送段FPGA还没开始拉高tx en前,接收侧已经看到rx er 时高时低,rx en持续为1,数据也不对。后来修改发送段enable信号使得常1,问题解决,rx er 不拉高,同时收到数据正确。但是实际情况,不能修改发送段代码,只能修改接收侧,请问怎么改,enable信号改成接收到数据前才打开enable?