Hi,您好,想确认一下,940pattern模式配置下的分频器控制寄存器0x03应如何选择,配置出来的频率与输出的MIPI clock有什么样的关系,谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,您好,想确认一下,940pattern模式配置下的分频器控制寄存器0x03应如何选择,配置出来的频率与输出的MIPI clock有什么样的关系,谢谢

您好,PCLK = M/N*(Oscillator Frequency)),而PCLK的大小决定了视频分辨率的大小。

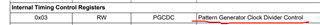

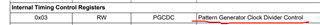

因为我们在做pattern test时候,如果不外加PCLK,可以使用内部晶振去配置,所以可以通过配置分频系数M/N 来获得想得到的PCLK大小。

除了sDS90Ux941AS-Q1, DS90Ux949-Q1, DS90Ux949A-Q1, DS90Ux929-Q1,和 DS90Ux947-Q1之外,其他器件的M 都为1.

对于940来说,内部晶振是140Mhz,如果我们需要PCLK为96MHz的话,N可以配置为2,这样得到PCLK为100Mhz。

同样比如941内部晶振是200Mhz,要得到800x480的分辨率,那么PCLK需要25Mhz即可,因此可以配置为M=1,N=8,即200*(1/8)=25hz。

您好,抱歉,是的940内部时钟为140MHz,我误当成200Mhz了,N=2的话 ,计算出来为70Mhz。

PCLK是Soc输出给serializer的频率,也可以理解成serializer恢复出来的PCLK。 那么对于940来说,PCLK和CSI-2 clock的关系:

fCSI =fPCLK*14/ Nlanes。 举个例子,如果PCLK=170MHz,4 lane data,那么fCSI=595MHz。

是的,PCLK的意义都是一样的,不论是外部给的,还是采用内部时钟产生的。

我找到了这篇关于深度理解FPDlink速率的应用手册 ,并且是中文版的,您可以参考下,有什么问题可以随时讨论,相信能帮助理解:

是的,这样计算,通常一个像素就可以传输RGB888或者其他数据格式。

不同的是,数据格式不同,数据的吞吐量不同,比如total data rate=PCLK * color depth。比如24bit,148.5MHz PCLK,total data rate=148.5*24.