您好,

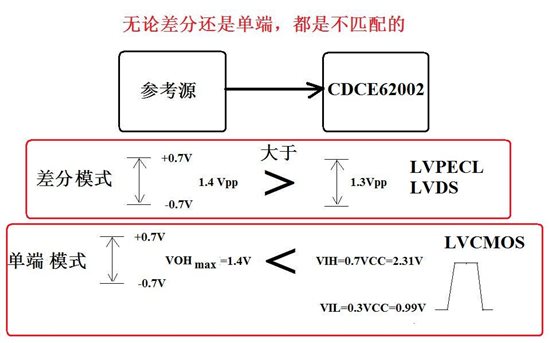

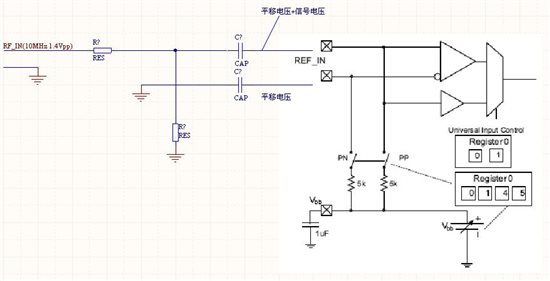

最近项目工程涉及时钟信号产生的工作。选用了CDCE62002用来把参考原子钟10MHz(1.4Vpp即±0.7V)单端输入正弦信号再生出800MHz左右的高频时钟信号来驱动后级数字电路。

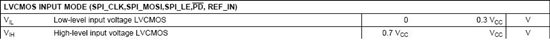

问题:1、62002REF_IN支持的LVCOMS高电平识别电压为0.7VCC即2.3V,10MHzRF信号显然无法触发逻辑‘1’。

2、对于62002datasheet上的LVCOMS的说明也有不明白的地方,还请指教。

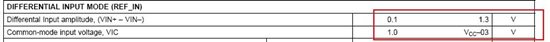

上图中数据在datasheet中p10。明确指出的高低逻辑电平的大小。而在p9中又有对REF_IN的输入描述,差分电压可以从0.1-1.3V,如下图所示。

这其中前后是否存在矛盾?

3、如何做到上述RF参考时钟的单端输入?能支持单端输入的好像只有LVCOMS规格吧,LVPECL、LVDS能支持单端输入么?需要做什么变换么?

望能答复,谢谢,辛苦了。