Other Parts Discussed in Thread: PLL1706, DS08MB200

各位大神,

我想请问一个问题:时钟经过门电路会不会让jitter更差。

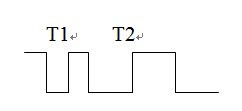

我的理解是这样的:门电路的tpd一般是会变化的,时钟经过门电路后,如果tpd在不停地变化,譬如从2ns~6ns。加入输入时钟是24.576MHz,那么T=40.7ns。考虑极限情况,前半周期tpd=2ns,后半周期tpd=6ns。

明显看出时钟频率变化。jitter明显增大。

可是我在TI的PLL芯片中也看到有门电路,如PLL1706,其中就有复用器。

请问我的理解是否正确?在音频电路中经常会是使用双时钟(22.5792MHz和24.576MHz),我现在使用的切换方案是使用复用器,请问这样可不可以,有没有更好的方案?谢谢!