Hello

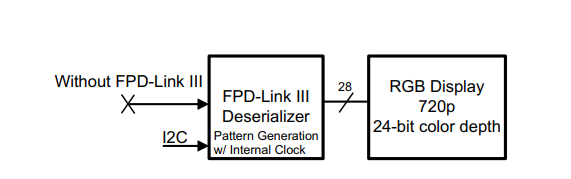

When using 948q1 (no serializer) test pattern , we were able to display the test screen normally on the screen, but the pixel clock is incorrect .

Internal Test Pattern Generation configuration mode

Desired pixel clock:2048 * 781 * 60 =95.96MHZ,we use Dual Link OpenLDI Output,so clk1 = clk2 = 47.98MHZ.

The configured internal clock:140MHZ / 3=46.66MHZ.

The actual measured pixel clock:CLK1 = CLK2 = 8MHZ.

Partial register configuration:

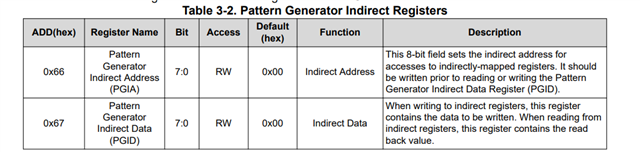

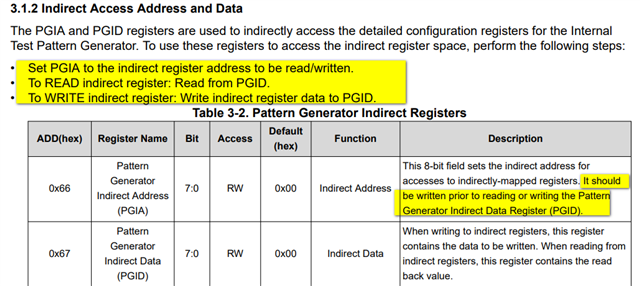

{0x66,0x03},

{0x66,0x03},

{0x63,0x01},

{0x64,0x41},

{0x65,0x04}.

Where is the problem?