Part Number: SN65DP159

Other Parts Discussed in Thread: TDP142

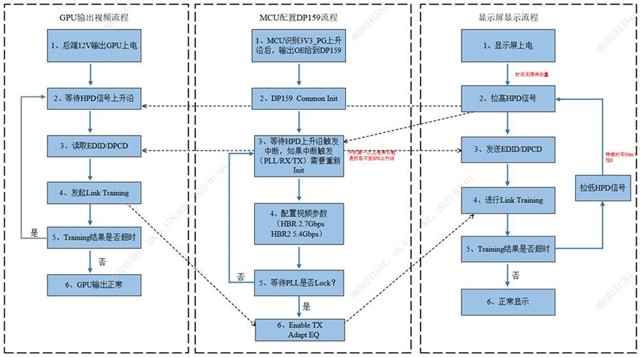

目前我们有在使用DP159 retimer这个芯片,这个芯片主要用于DP信号的加强,我们在使用这个芯片时碰到以下几个问题:

- DP159完成PLL Locked的时间一般是多久,以及最大的等待时间建议是多少,没有完成PLL Locked是否需要重新完整配置一遍DP159?

- 偶发开机上电,显示屏No Signal,抓取MCU配置DP159的IIC数据,发现读取DP159的LOCK_COMPLETE status,结果是0xE3,是Locked状态,但没有显示,显示屏一直发送HPD 的unplug信号,MCU反复配置仍然没法显示,这个算是DP159的异常状态吗?

- Xilinx有一份用于配置DP159的C文件,c、xdprss_dp159.h见附件,里面的配置流程与规格书推荐的基本一致,但是不同阶段部分配置寄存器种类有差异,需要现场支持解释一下对应的功能和影响,特别是针对DP159的配置寄存器的含义;

- 规格书推荐的DP159寄存器配置,只有一个回读的寄存器LOCK_COMPLETE status进行状态确认,其它的全为写入操作,如何确保寄存器配置成功,LOCK_COMPLETE status置位即可认为配置成功?

- datarate、lane count、sink removal or DP Source no longer detected,推荐配置部分寄存器即可,如果重新完整配置一遍(相当于上电初始化),有没有问题,对于DP159的此次上电的正常工作有无负面影响?

以下是我们固件的配置流程: