Part Number: DP83TD510E

I am having problems using DP83TD510E.

Environment:

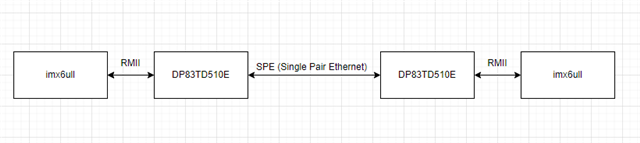

DP83TD510E works in rmii slave mode. Soc provides a 50Mhz clock to the xi pod.

CRS_DV/RX_DV Pin 18 is configured as CRS_DV (default).

Receiver with tapping at 50 Ω (Recommended).

The id of the phy chip is set to 0.

linux system from the following github link.

https://github.com/nxp-imx/linux-imx/blob/lf-6.1.y/drivers/net/phy/dp83td510.c

The DP83TD510E is always in the Link is down state, and I don't know how to deal with it. The DP83TD510E has been registered.

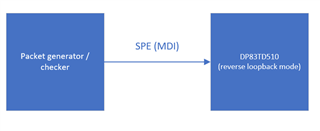

I tried to test Loopback Modes, but I still don't know how to handle it.