Part Number: DP83867CR

MDIO信号电平接上PHY后电压为1V,断开PHY后电压正常为1.8V,是什么原因造成这样的呢,附上原理图DP83867 PHY.pdf

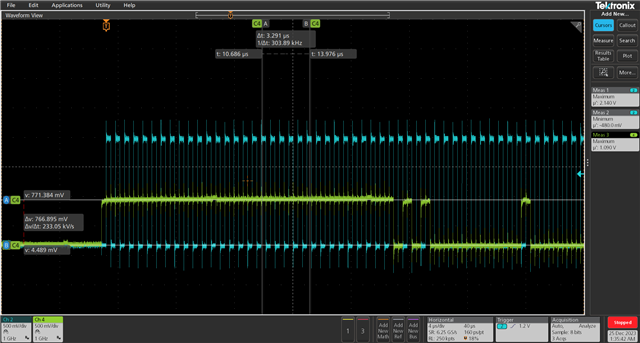

图一

图一

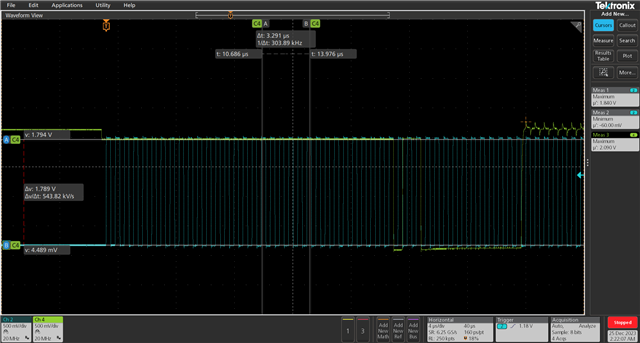

图二

图二

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

抱歉给您回复晚了。

我想和您确认下,您指的“MDIO信号电平接上PHY后电压为1V”,也就是说MAC和DP83867 通信时电压会从1.8V降至1V是吗?

如果断开MAC,测量DP83867的MDIO电压为1.8V? 因为我看MDIO上拉2.2K到1.8V了。

其他引脚电压都正常吗?

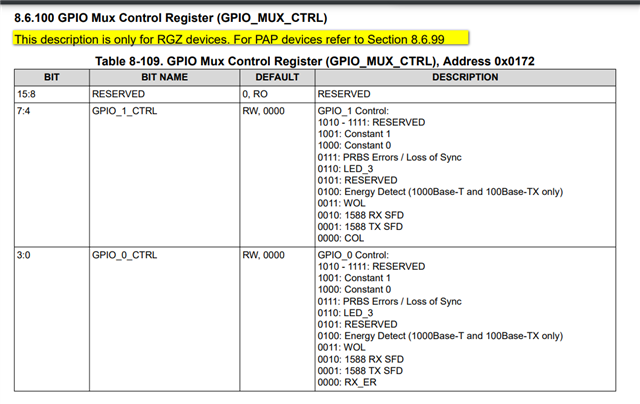

您好,您使用的是DP83867的PAP封装还是RGZ封装?因为RGZ封装的话,GPIO的功能是通过GPIO_MUX_CTRL配置的。

但是这个不适用于PAP封装,所以我担心是RGZ封装,GPIO的功能是根据这个寄存器配置决定的,从而影响MDIO。

否则理论上来说,GPIO就是通用GPIO口,不会影响到MDIO。

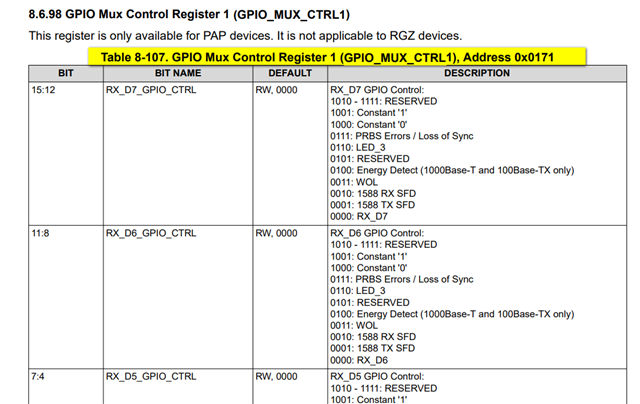

这个寄存器和PAP封装有关,我们这边没配这个寄存器,是不是默认配置了?

是的。没有配置就是默认的,或者说即使配置了,使用RGZ封装也不会改变GPIO的功能。这个寄存器对RGZ封装不起作用

我看着后面一个寄存器和RGZ(我们所使用的封装)相关,我外部上拉(GPIO0和GPIO1均上拉)后内部如何配置才能避免影响MDIO的情况。

是的,上面附图我附错了,应该是这个寄存器。因为您提到悬空GPIO可以解决问题,而GPIO内部已经下拉,所以外部悬空相当于一直保持低电平。

所以这里7:4 和3:0 都配置为1000: constant 0,常数0。相当于外部GPIO 悬空处理。您验证下是否能解决您的问题。