Part Number: SN65MLVD206B

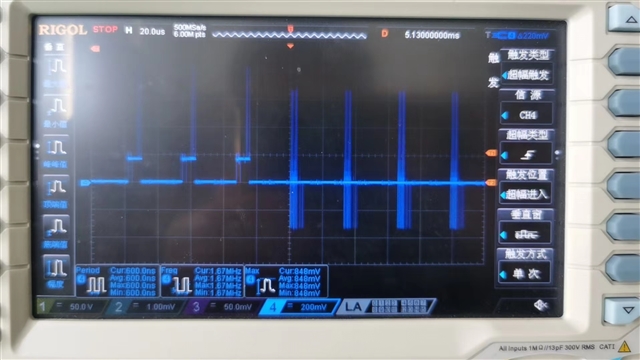

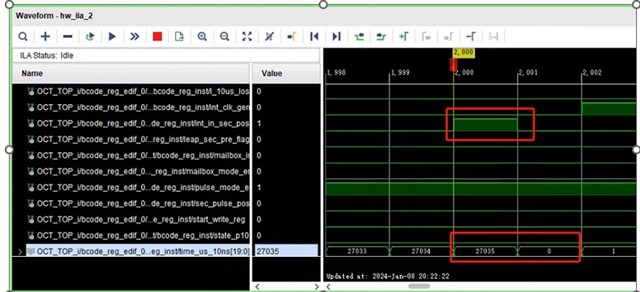

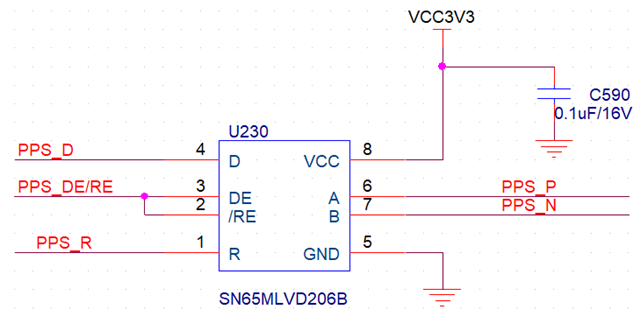

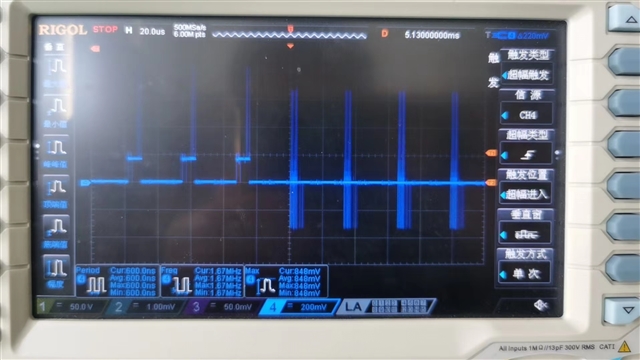

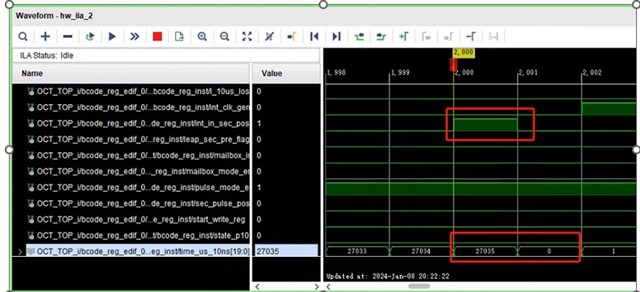

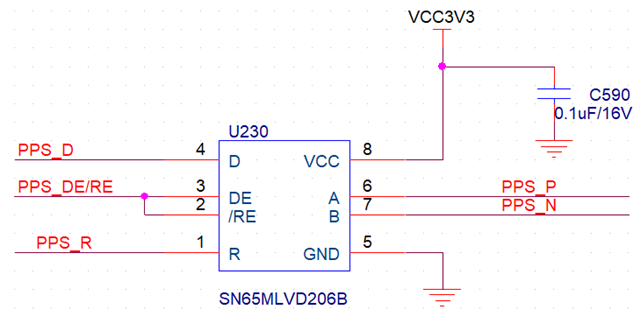

测试环境为断开输入的差分信号(芯片6,7脚断开),芯片供电正常,用途仅用作差分转单端信号输入FPGA,原理图如下,在FPGA内部抓数中可以抓到一个10ns左右的高电平信号,用示波器抓可以抓到一个600多mv的毛刺(监测的是芯片的输出1脚)。

1.将DE/RE和D均接地拉低,也会触发毛刺。

2.去除芯片查看FPGA内部抓数未抓过此高电平信号。

测试情况看很像是芯片内部的问题,我想问一下是什么原因导致的,如何能尝试解决,谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65MLVD206B

测试环境为断开输入的差分信号(芯片6,7脚断开),芯片供电正常,用途仅用作差分转单端信号输入FPGA,原理图如下,在FPGA内部抓数中可以抓到一个10ns左右的高电平信号,用示波器抓可以抓到一个600多mv的毛刺(监测的是芯片的输出1脚)。

1.将DE/RE和D均接地拉低,也会触发毛刺。

2.去除芯片查看FPGA内部抓数未抓过此高电平信号。

测试情况看很像是芯片内部的问题,我想问一下是什么原因导致的,如何能尝试解决,谢谢!

我目前的设计是一个幅值为3.3v的高电平(1秒1次)直接输入给SN65MLVD206B转成差分,差分在通过另一个SN65MLVD206B最终转换成单端信号输出,不考虑其它因素的情况,这种方案是否可行,不外加电路的情况自行输出的差分信号是否直接满足芯片的参数标准?