Part Number: ISO7741

TI的专家你们好

目前再用到贵司的ISO7741电机驱动和通信隔离,请教下隔离器底下PCB要开槽吗?开槽的话,宽度怎么衡量?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

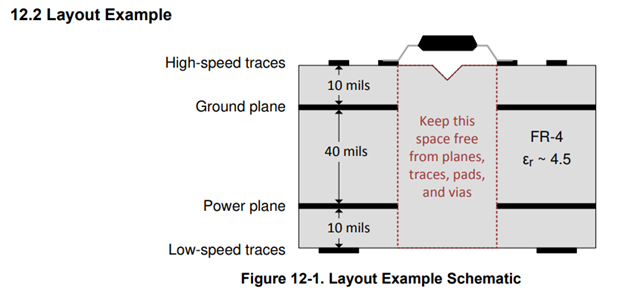

您好,您是指的datasheet这里中间一块空的区域吗?

这里指的是在器件下方的 PCB 需要保持没有任何布线或过孔,以实现完整的器件隔离规格。 除了ISO7741,其实任何隔离器满足所需爬电距离/间隙的要求。 如果隔离或爬电距离/间隙要求较低、则间距可以减小。这是因为空气在较高的电压下会发生电介质击穿、从而导致高电压从 GND1传递到 GND2。 需要保持一定的间隙,以便在不发生空气击穿的情况下能够容忍高压 的浪涌事件。 如果此间距减小,空气击穿电压也会降低。

可以在芯片下方进行凹槽设计,以增加通过 PCB 的爬电距离。下面这个帖子详细介绍了爬电距离的要求:

您好,关于如何确定爬电距离/间隙值,我还没有去查看更多的资料去研究,但是给定应用所需的爬电距离和间隙在很大程度上取决于特定用例的行业标准以及需要的隔离级别。

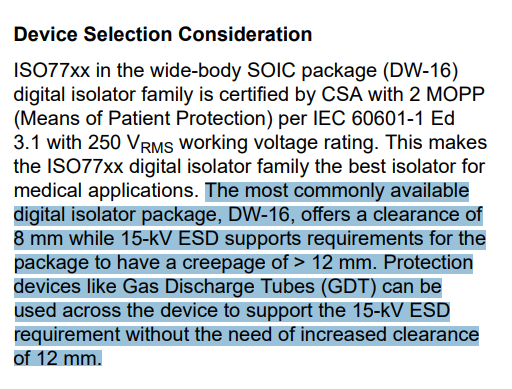

我查找了下一些应用手册以及我们精度实验室的讲解视频,介绍了不同行业标准的爬电距离设计要求,比如8mm或者10mm的爬电距离是否合适。

这篇关于隔离器的应用手册介绍了根据不同封装下的爬电距离:www.ti.com/.../slla608.pdf

在关于隔离器的视频介绍中,第6部分介绍了什么是爬电距离/间隙。您可以先看看下,如果有什么问题再联系:

https://www.ti.com/video/series/introduction-to-isolation.html

爬电距离/间隙这个明白,主要是想了解这个凹槽的宽度一般怎么考虑?比如1mm 和2mm凹槽,其实爬电距离影响应该甚微。

好的,关于凹槽宽度,我这边查下资料,或者去和资深工程师确认下。

不必客气,关于凹槽宽度,正在确认中,如有收到答复,会尽快通知给您。

顺祝假期愉快。

另外再请教下ISO7741 规格里面的VISO,VTEST = VISO,t = 60s 这个测试时,测试漏电流设定的门限是多少?

您好,关于凹槽宽度,我这边已经确认:

在 PCB 中切割凹槽有助于增加爬电距离、但我们没有为隔离器指定任何特定的宽度。因为这在很大程度上取决于系统。 任何系统所需的最小爬电距离由相关行业标准定义,因此所需的额外爬电量取决于隔离器的爬电距离与标准要求的比较情况。 但是,对于宽度大于1mm 的凹槽,现有爬电距离加上凹槽宽度和凹槽深度的两倍必须等于或超过所需的爬电距离。 槽的大小也不应足以削弱或损坏 PCB 基板,否则可能导致机械测试故障。

这个问题也请帮忙确认下,谢谢

好的。

抱歉,回复晚了。

VTEST = VISO,t = 60s 这个测试时,测试漏电流设定的门限是多少?

测试VTEST = VISO,t = 60s 这个测试时,测试漏电流设定的门限是100uA。

非常感谢!再请教下,为啥是100uA?或者这个100uA是基于什么考虑的?

好的,我这边再去确认一下。如有回复,尽快通知给您。

您好,我这边已经确认,工业标准典型的这个漏电流门限大约是10mA,而我们TI测试使用的阈值为100uA。

10mA是系统级测试工频耐压限流设定值,TI考核数字隔离器测试工频耐压为啥是100uA?基于什么理论还是?

您好,您还有其他问题吗?

关于这个漏电流门限的问题,我昨天和美国那边也是反应了,基于什么考量的,他们给的回复就是上面我的回答。

如果您仍有疑问的话,也可以将问题提交到英文E2E进一步咨询。

那如果测试下来和datasheet 有偏差,可以将测试流程描述下,我这边帮您再去确认。

主要是贵司datasheet标称VISO这个参数里面没有写这个100uA,

测试方法就是将ISO7741的2侧分别短接,使得器件成一个2端网络,在2侧施加1分钟的工频交流电源。

您好,施加1分钟的工频交流电源是多大电压的?另外,测试下来远小于100uA,那您这边测试电流为多少?

30uA以下;另外请教下下贵司测试隔离器VIOSM这个电压时,浪涌发生器的输出阻抗是设定多少Ω测试的?

您好,抱歉上周休假了,由于您的问题很久了,为了能够尽快给您答复,建议您重新再发个帖子,我们会尽快给您答复。