Part Number: SN74LVC1G125-Q1

Other Parts Discussed in Thread: SN74AVC16T245

您好:请问SN74SN74LVC1G125这个芯片,OE引脚拉低,然后输入悬空,请问输出时什么状态呢?谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN74LVC1G125-Q1

Other Parts Discussed in Thread: SN74AVC16T245

您好:请问SN74SN74LVC1G125这个芯片,OE引脚拉低,然后输入悬空,请问输出时什么状态呢?谢谢

您好,

SN74LVC1G125-Q1是CMOS输入器件,未使用的输入必须保持在VCC或GND 以确保设备正常运行。否则的话,输出可能会振荡或烧毁器件。

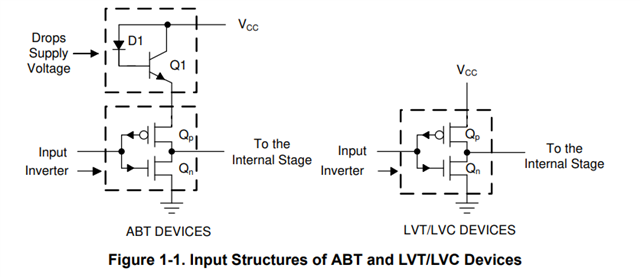

CMOS输入结构是由一个到VCC的p-通道和一个到GND的n-通道组成,如上图所示。低电平输入时,P通道晶体管打开,N通道关闭,导致电流从VCC流动,并将节点拉至高电平。高电平输入时,n通道晶体管打开,P通道关闭,电流流向GND,使节点处于低电平。在这两种情况下,没有电流从VCC流向GND。但是,当从一种状态切换到另一种状态时,输入会越过阈值区域,导致N通道和P通道同时打开,从而在VCC和GND之间生成电流路径。此电流浪涌可能具有破坏性,具体取决于输入处于阈值区域(0.8 V至2 V)的时间长度。

因此,CMOS输入器件输入端不能悬空,以避免输入电平不确定造成输出振荡或上下管同时导通而烧毁器件。

接GND不需要串电阻,接GND芯片一直是使能状态。

如果您需要一个控制管脚控制OE的高和低的话,那么就需要一个上拉电阻接至VCC,因为在控制管脚输出低电平使能芯片的时候,如果不串联电阻,而控制器吸收电流的能力又没有那么大,大电流会烧掉这个控制管脚的。和下面帖子的工作原理一样:

https://e2echina.ti.com/support/logic/f/logic-forum/558646/sn74avc16t245-sn74avc16t245