工具与软件:

我的客户在问这些问题。

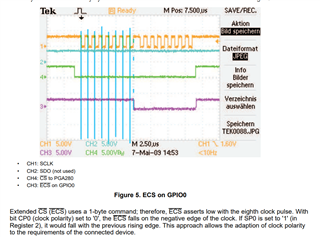

PGA280规范(SBOS487B-2009年6月- 2020年3月修订、第24页)表明、CP0 =1会导致 ECS_N 在 SCLK 负沿或下降沿之后下降(从第7.4.1.1节)。 您在上一篇文章中链接的应用手册表明、CP0 =0会导致 ECS_N 在 SCLK 负沿或下降沿之后下降(图5)。

哪种文档是正确的? 我的客户希望 使用 SCLK 下降沿、那么 CPO 应该设置为0还是1?

此外、本应用手册的图5将 ECS_N 设置为在 SCLK 的上升沿生效。 我们是否有 更好的 ECS_N 图、该图显示了 SCLK 下降沿与 ECS_N 置位之间更准确的 Tpd?