主题中讨论的其他器件:PSPICE-FOR-TI、 TINA-TI、 TLV3605、

工具/软件:

您好的团队、

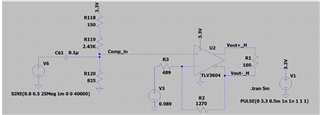

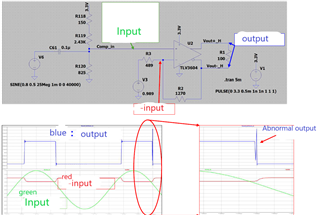

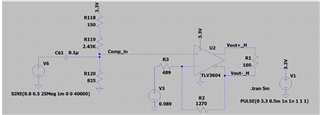

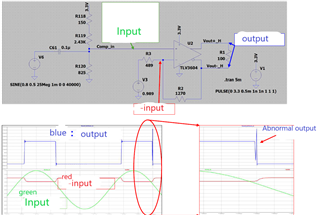

构建以下电路时、发现在下降沿产生了异常波形。

仿真中也会出现同样的情况。

发生这种情况的原因是什么?

此致、

Ryu。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好的团队、

构建以下电路时、发现在下降沿产生了异常波形。

仿真中也会出现同样的情况。

发生这种情况的原因是什么?

此致、

Ryu。

尊敬的柳山:

抱歉、我无法帮助使用 LTSpice 解决问题。 您是否可以使用 PSpice-for-TI 或 TINA-TI 重新构建电路、以查看您是否遇到相同的问题?

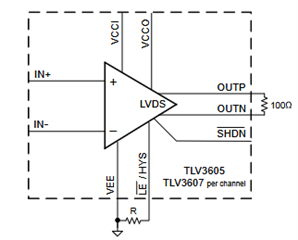

是否可以将 TLV3604替换为 TLV3605? TLV3605具有可通过 LEBAR/HYST 引脚控制的~60mV 内部迟滞。 这样、就没有加载 LVDS 输出 Q 和 Qbar 的反馈路径:

尊敬的柳山:

这种质量使在示波器图像上看到文本变得有点困难。 在示波器结果中、比较器的输入是什么? 他们被调查了吗? 如果是、您是否看到任何脉冲输入超过一次?

我很好奇、想知道使用周期性输入时输出是什么样子。 您分享的示波器结果似乎只有一个脉冲。 您能否用周期信号(如正弦波)来测试电路、看看是否在每个输出脉冲中出现了这种异常波? 您是否还能改变频率以查看异常波是否也出现在那里?

这是否意味着反馈引起的振荡是可能的原因?

迟滞的实现是正反馈、因此通过设计应该可以抑制输出端的振荡(抖动)。 您能否通过移除 R2 (反馈电阻器)并查看异常波形是否仍然出现来尝试消除迟滞?