Other Parts Discussed in Thread: OPA210

工具/软件:

尊敬的 TI-PSPICE 团队

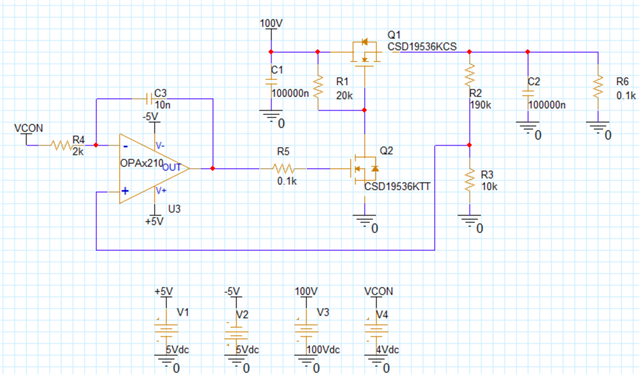

我使用 TI-PSPICE 为客户模拟高压分立式线性稳压器。 但是、即使更新了仿真条件、我也会遇到收敛问题。 您能帮助解决收敛问题吗? 下图所示为我的原理图。 还在此处附上了我的原理图文件、用于调试问题。 非常感谢!

此致、

Bill

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、Raymond

感谢您的支持。 VCON=4V 时、采用电压的系数为20、因此预期输出电压为80V。 输出电流需要大于2ADC 的大电流和大于10A 的瞬态电流。

是的、PMOS 在此处易于驱动。 但 TI 的 PMOS 无法承受超过100V 的电压。 此外、在市场上、NMOS 的选择比 PMOS 更多、因此、我更喜欢在此处使用 NMOS。 此处中的 R1为 Q1提供了一个潜在的 DIVE 通道。 也就是说、R1和 Q2构建了一个分压器并驱动 Q1。

如果您还有其他问题、请告诉我。 谢谢。

此致、

Bill

尊敬的 Bill:

电路有问题。 当100VDC 通电时、Q1开启、输出约为94VDC。

误差放大器连接在同相节点上、由于~-5V 的负栅极电压、Q2永远不会开启。

e2e.ti.com/.../80Vdc-Series-Regulator-Not-Working-05092025.TSC

您需要找到一种方法来控制 Q2的栅极电压。 对于此类串联稳压器、通常使用负反馈。 因此、这里没有积分器、它需要有误差放大器(设计中的积分器)。 这种收敛可能与 OPA210的配置有关、您不需要在该电路中使用高端运算放大器。 通用 或常规精密运算放大器可以用作误差放大器。

基准电压是串联稳压器中最重要的部分。 它会有噪声、输出会 有噪声。

如果您有其他问题、请告诉我。

此致、

Raymond

嗨、Raymond

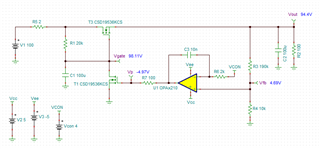

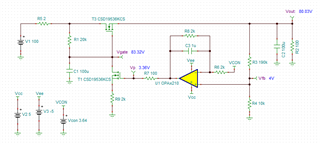

电路似乎没有问题。 让我们做一个分析草案。

1、如果输出高于预期、则误差放大器的同相输入将高于预期、误差放大器的输出将会变化更高。 这将导致 Q2的 D 极 下降。 然后输出电压将为低电平。

2、 如果输出低于预期、误差放大器的同相输入将低于预期、误差放大器的输出将变低。 这将导致 Q2的 D 极点 上升。 然后输出电压会更高。

因此、它是一个负反馈系统。

下面是我使用其他软件的仿真结果。

此外、还附有仿真文件以供参考。

请告诉我您的意见。 谢谢。

此致、

Bill

尊敬的 Bill:

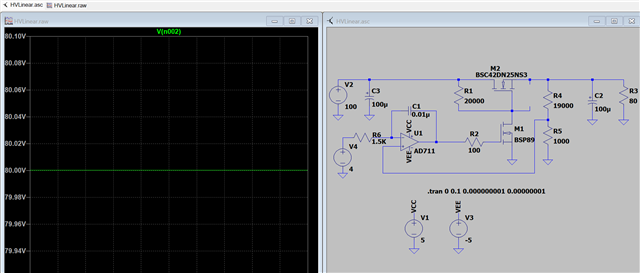

当输出与设定点不同时、您只分析两种情况。 当 V_error = 0时会发生什么情况、这就是真正需要积分器的地方。 如果电路需要进行精确调节、则需要为反馈环路的误差放大器提供真正的积分器。 尝试在输出端注入脉冲负载、并查看稳压器的行为。 我认为这将会振荡。

我无法通过 E2E 使用 LTSpice 仿真。 但是、您有一个积分器、将 V_feedback 节点馈送到同相节点。 通常情况下、它是相反的。 电路可能存在稳定性风险。 我回顾过、Vref (例如4.00V)应该连接到同相输入、该节点上的噪声在稳压器输出端增益、而不是衰减(我认为这就是您得到的)。 必须进行循环分析才能找出这个问题。

如果您有其他问题、请告诉我。

此致、

Raymond

尊敬的 Bill:

我忘记提到 LTSpice 在默认情况下使用了非常宽松的收敛标准、例如 RELTOL、VNTOL、ABSTOL、而不是 PSpice 或 Tina 仿真环境。 在这方面、TINA 优于 PSpice。 您可以更改这些默认设置、但我更喜欢使用 Tina 仿真器。 在模拟直流稳压器和开关稳压器方面,LTSpice 具有一些优势(更好的非线性仿真模型,允许集成模型和优化)。 但请注意、当您将电路一起放在电路板上时、这并不意味着电路可以工作(您仍需要对许多此类电源电路进行微调)。

此致、

Raymond