工具/软件:

您好:

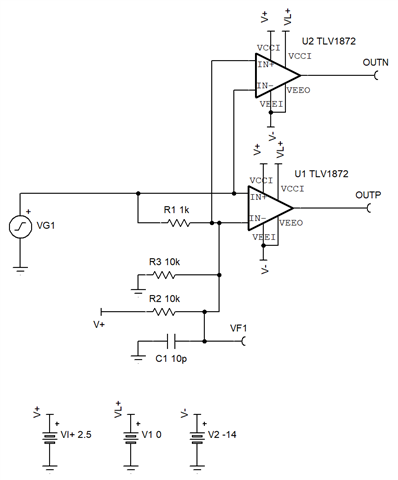

我计划将 TVL1872 比较器用作具有数字输入的互补输出驱动器。

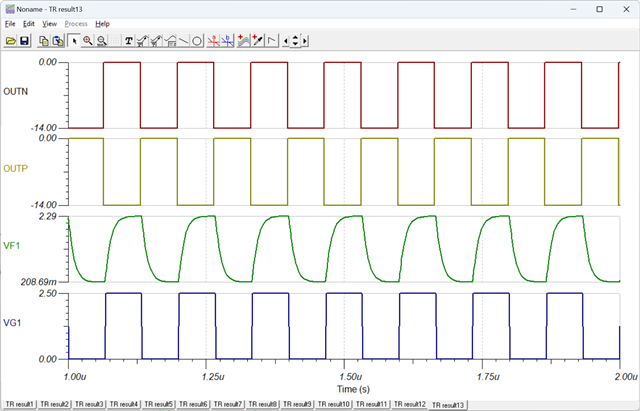

两个输出在 0V 和–14V 之间切换、但输入是数字输入、例如 2.5V CMOS。

对于这种情况、您是否有任何推荐的电路?

从数据表中可以看出、将比较器阈值偏移 得较低似乎更好、从而实现更大的过驱和更小的欠驱动。

但我想使用互补输入(一侧反相,另一侧同相)。

这是否意味着负输入翻转过驱/欠驱要求?

换句话说、使用 2.5V CMOS 输入信号时、您是否会将一个输入偏置在 0.2V 左右、将另一个输入偏置在 2.3V?

(最小/最大 2.5V CMOS 输出电压。)

这使输入触发电平不对称、但如果有更简单的方法、请告知我。

以下是其他一些详细信息:

VEEI = VEEO =–14V

VCCO = 0V

VCCI = 2.5V (或?)