工具/软件:

您好的团队、

客户正在使用 TAS2505。 如果采样率为 22.05kHz、位深度为 16 位、应如何设置音频 MCLK 和 BCLK? 您能否提供相应的 PLL 寄存器设置?

谢谢

Xiaoxiang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好的团队、

客户正在使用 TAS2505。 如果采样率为 22.05kHz、位深度为 16 位、应如何设置音频 MCLK 和 BCLK? 您能否提供相应的 PLL 寄存器设置?

谢谢

Xiaoxiang

嗨、Xiaoxiang、

BCK = FSYNC *通道数*每个通道的位数。

现在、客户能够根据 FSYNC = 22.05kHz 和每通道位数= 16 位来计算 BCK 频率。通道数将基于客户馈送到 IC 的 I2S 信号。 所有这些值都会决定 BCLK。 这类情况下不需要 MCLK。 此 IC 中的 PLL 通常处于自动检测模式。 还有芯片提供的片上 PLL 选项。

此致、

Ore.

嗨、Xiaoxiang、

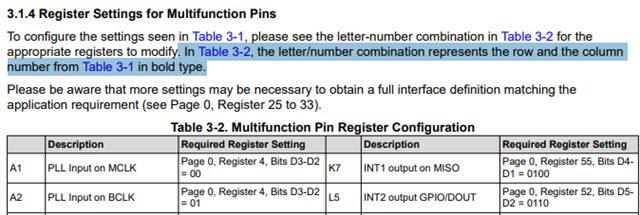

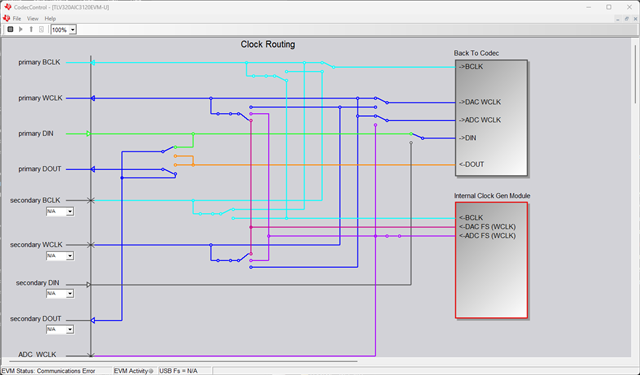

首先使用 A2 指令选择 BCLK 作为输入

您能否在主题中阐明您使用的通道数量? 还请说明位深度 16 位是否超出更宽的字宽? 例如、24 或 32 字宽的 16 位深度? 请也澄清这一点。

完成后、我可以引导您完成一个关于如何选择表 3-16 中的值以获得可正常工作的 PLL 树的破解。

如果未给出响应、我将认为该线程已结束。

此致、

Ore.

尊敬的 Xiaoxiang:

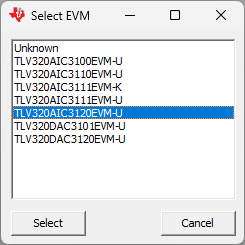

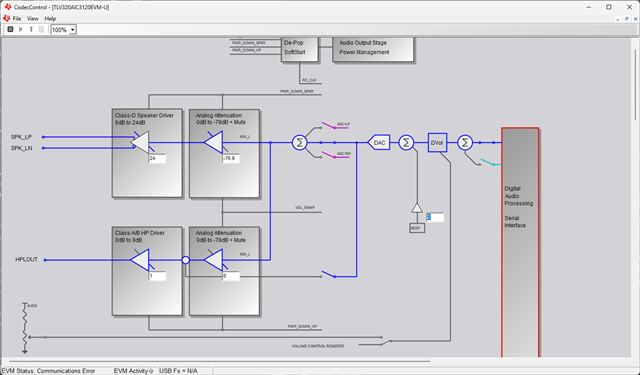

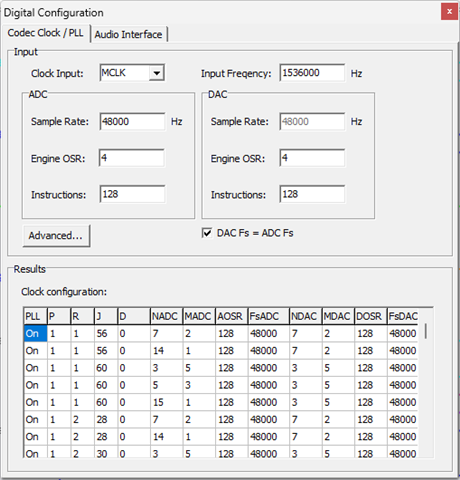

您可以从以下位置下载 AIC GUI: 评估模块 (EVM) 的 SLAC366 GUI |德州仪器 TI.com

这可用于计算 PLL 设置。

对于您指定的示例、请遵循以下说明:

如果您有任何问题、请允许我来看看。

此致、

-伊凡·萨拉扎尔

应用工程师