请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM62L-PROCESSOR-SDK工具/软件:

您好、

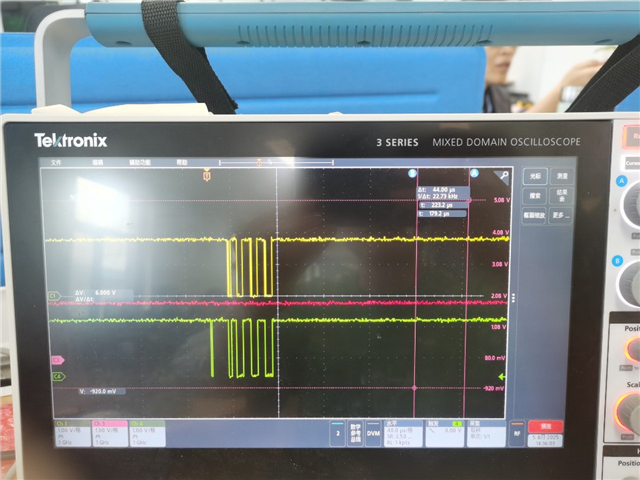

我们发现使用 CS0(连接到 8 线 NAND 闪存)和 CS1(连接到 4 线 NOR 闪存)可能会导致芯片选择冲突、如下图中 CS0 和 CS1 的波形所示。

将 TI EVM 替换为 CS0(连接到 8 线 NAND 闪存)和 CS3(连接到 4 线 NOR 闪存)后、它会正常工作。

CS0 和 CS1 为什么有冲突。