Other Parts Discussed in Thread: TLV3801, SN74AUC74

器件型号: TLV3801

Thread 中讨论的其他器件: SN74AUC74

大家好:

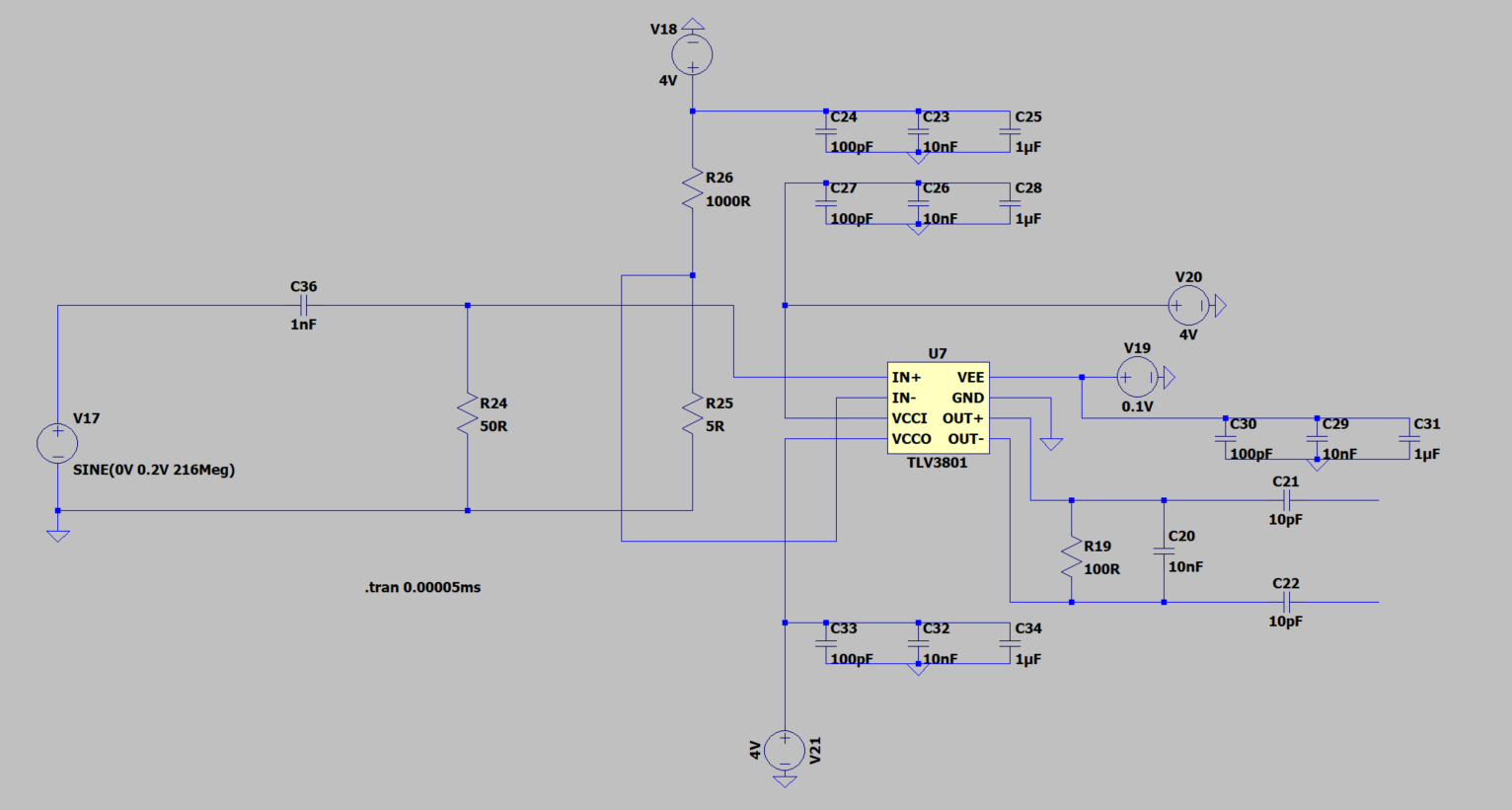

我目前正在尝试开发一个使用 TLV3801 的电路。 来模拟我使用 LTSpice 的元件。 基本思路是用高频 (216MHz)、低振幅 (200mV) 正弦波向 TLV3801 的同相输入馈电、以便在输出端生成 216MHz 方波。

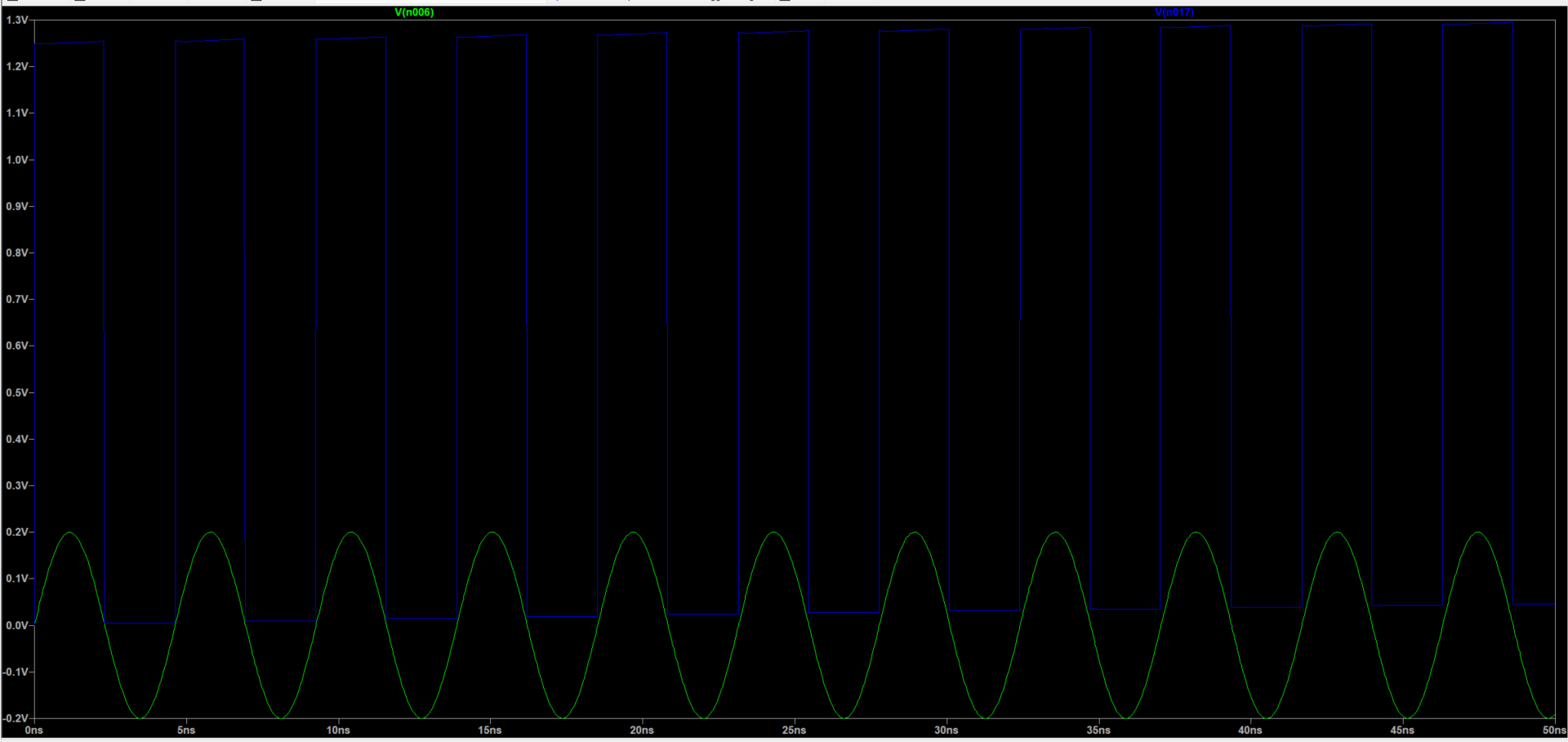

到目前为止、取得的成果看起来很有希望。 我添加了一些屏幕截图来显示获得的信号:

绿色信号是 216MHz 正弦波、蓝色信号是 TLV3801 的 OUT+引脚。 到目前为止一切顺利。 问题在于、在下一级、我需要将该方波馈入 D 型触发器 (SN74AUC74)、该触发器的工作电压约为 1.8V VCC。 因此、触发器的高电平输入电压约为 1.2V、这非常合适。 但根据其数据表、低电平输入电压约为 0.6V。 因此上述方波不能像这样使用、因为它实际上永远不会关闭 SN74AUC74。

所以我尝试了一点,通过稍微修改上面的电路,以某种方式获得了完美形状的方形信号,用于我的特定应用。 请参阅以下屏幕截图:

现在来看看实际问题 — TLV3801 的 VEE 值是否可以略高于 GND? 当我将 VEE 置于+100mV 左右时、电路似乎工作正常(请参阅上述蓝色信号)。 存在一点漂移、会导致 OUT+引脚上的较低值从 0V 缓慢增加至大约 120mV 的最大值、但该信号仍然非常适合我的用例。 如果 I 将 VEE 设置为–100mV、–50mV 甚至+50mV 或+200mV、OUT+引脚上没有信号。 因此、+100mV 似乎是一个甜蜜点。 这只是一个数字问题/不是一个现实的结果吗? 或者、即使明确不建议将 VEE 设置为 100mV(因为它超过了 IC 的最大额定值)、在技术上是否可以将其设置为 100mV?

如果我尝试使用另一个比较器下拉 TLV3801 LVDS 输出的下限阈值、我可能会争取额外的传播延迟、也不会像上面蓝色信号的边沿那样看到如此干净而锐利的方波。 因此、我想尽量避免使用大量额外的电路。 也许你们对这个问题有一些建议。

非常感谢您的时间和兴趣、

Laule