Other Parts Discussed in Thread: OPA564, TINA-TI

主题中讨论的其他部件: TINA-TI

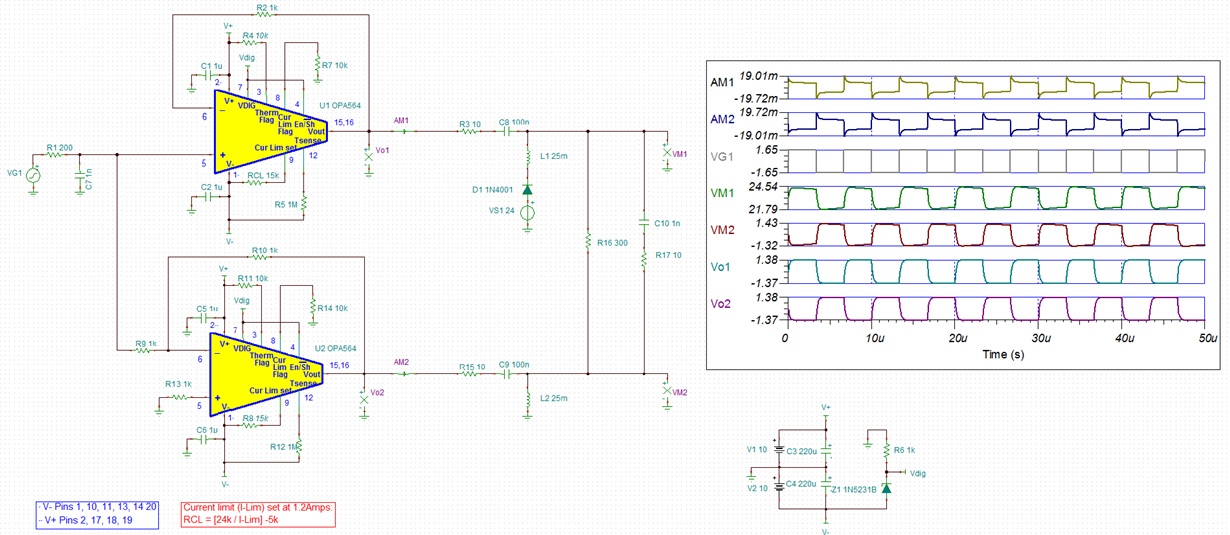

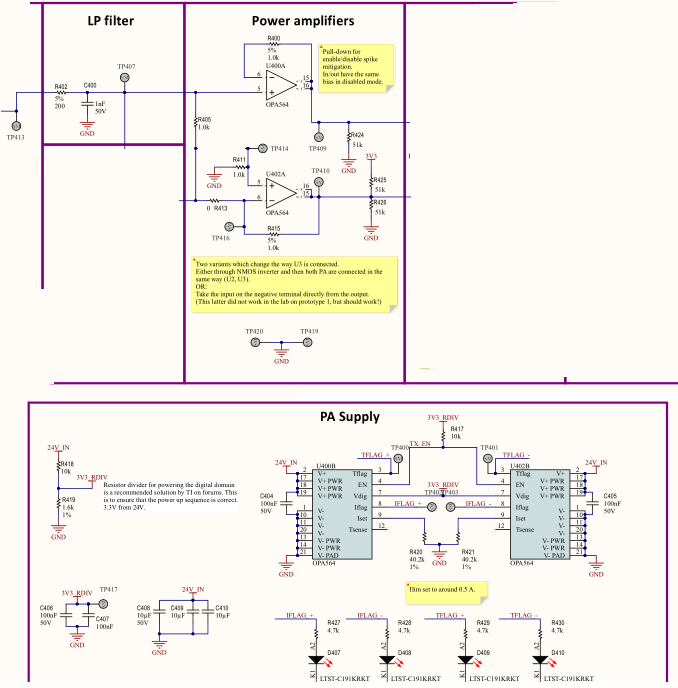

我正在快速制作一个原型,并且正在使用两个OPA564器件。

我正在尝试在24V电源线上实现PLC差分输出。

我有一个100-200 kHz的输入信号方波,具有3.3V振幅。

其中一个OPA564配置为缓冲器(用于+24V端),工作正常!

另一台设备被配置为简单的反相器,我根本无法使用此设备。

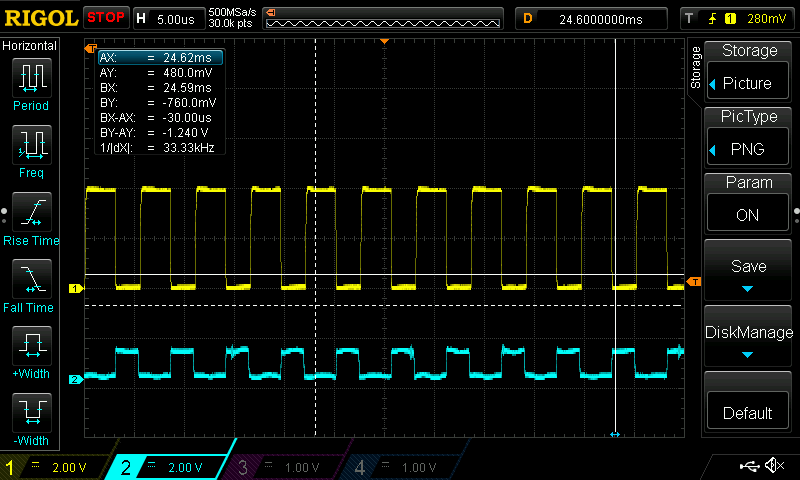

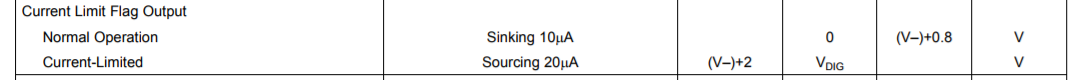

我在OC标记上看到脉冲,但它大部分是高的。即使我没有任何东西连接到输出或输入。

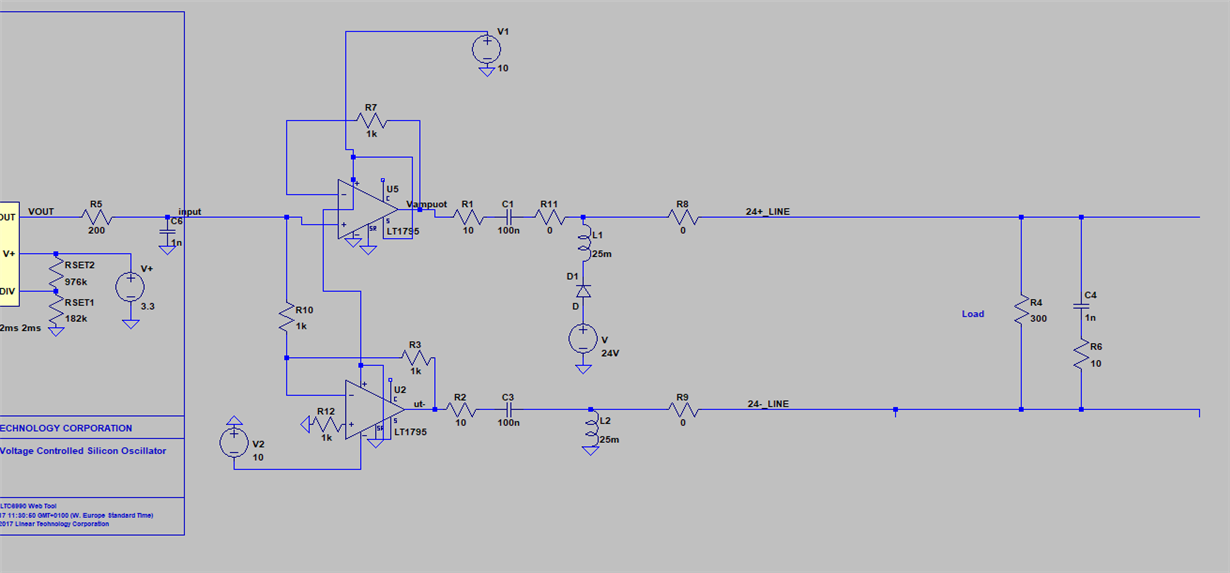

我将其连接为LTSPICE模拟(忽略奇怪的部分,制作可读原理图的工作非常糟糕,抱歉!)

但只需一个10V电源。 (由于无法正常工作,尚未将任何输出连接到它)