主题中讨论的其他器件: OPA855

您好!

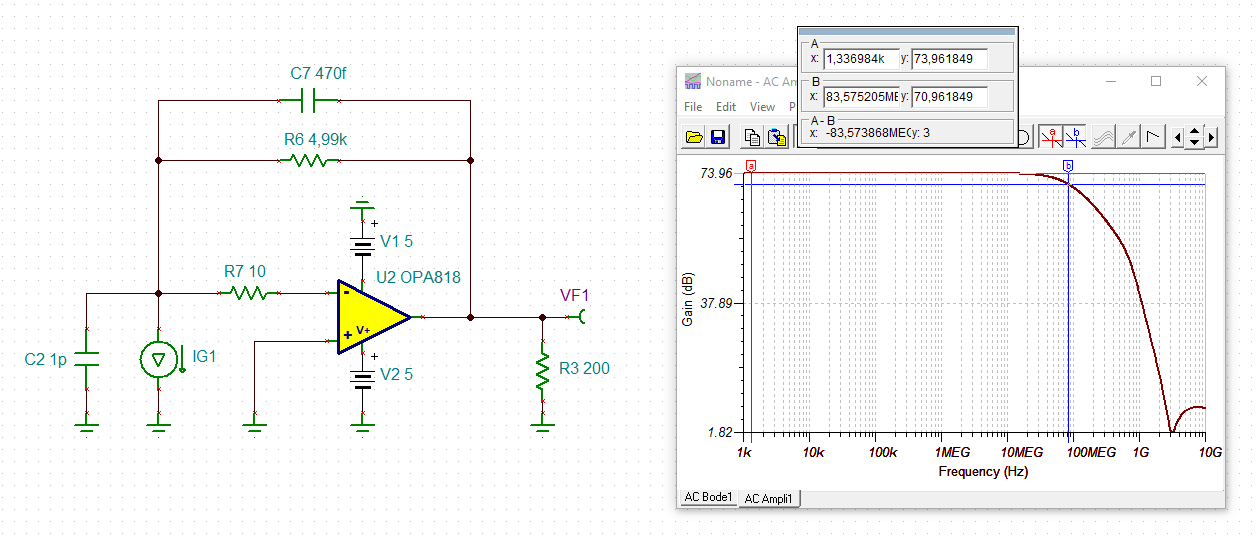

我以前曾问过这个问题,不幸的是,我似乎无法成功地进行这种衡量。 我有一个具有5k Ω 增益的 TIA、该 TIA 通过高速光电二极管(连接到 PCB)连接到裸片。 我们具有大约1-50MHz 的所需信号。 根据 PD 制造商的说法、二极管应具有低于 pF 的电容、由于我们只需要最大50MHz 的频率、因此我们添加了一个33pF C 来限制带宽。

左侧的大黄色块将包含光电二极管、并闭合环路。 在我们的测试板中、我们还没有光电二极管、我们通过0欧姆电阻器闭合 PD 连接 PCB 上的环路。 与818的反相输入上的33pF 相比、二极管的电容应该很小、因此我希望我们可以在没有 它的情况下测试电路。 遗憾的是、我无法很好地同意我预期的跨阻增益(5k)~ 74dB。 我们有 MMCX 连接器、因此可以清晰地过渡到 VNA 电缆。 我们为"分流电容器"选择了1nF 和4pF、并将输入和输出匹配为50欧姆。

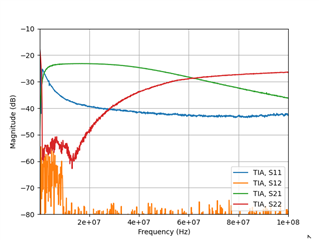

s 参数如下所示:

是否有人可以提供一些指导、说明我们如何从这条曲线返回到互阻抗曲线?

如果有任何帮助、我们将不胜感激!

此致

Dominik