你(们)好

当在我们的效应器产品的差分至单端电路中使用 TLV9062时、会出现技术问题。 某些有缺陷的型号在48V 幻象电源断电时会出现输出毛刷现象、更换 tlv9062后、这种现象将消失。 详情如下:

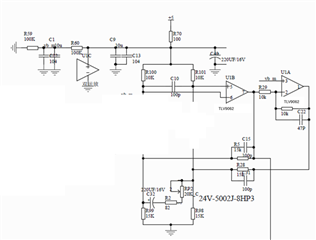

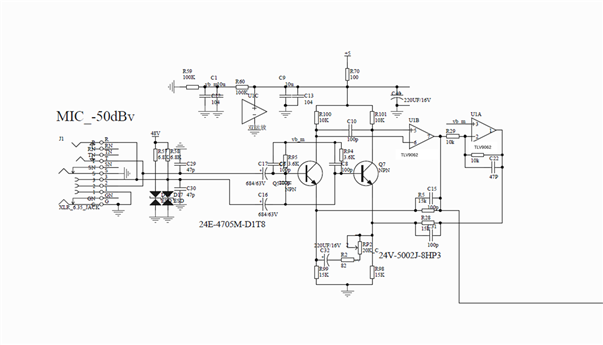

系统原理图如下:

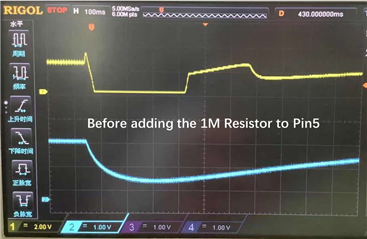

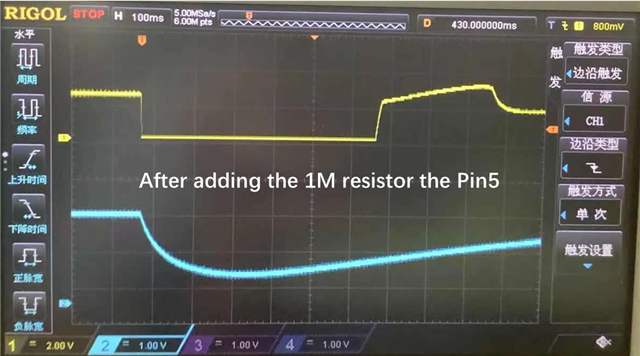

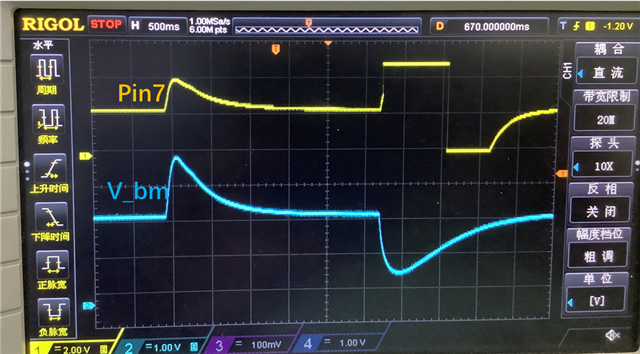

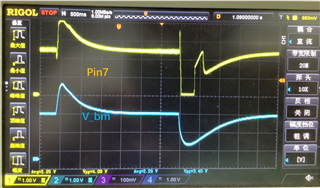

2. 当48V 幻象电源通电和断电时,由于电容器的充电和放电,VB_ M 将出现压降或上升现象,如波形中的蓝色波形所示。

在我们的测试结束后、发现当48V 电源关闭时、tlv9062的引脚7输出的音频端口将出现问题。 进一步抓住波形、发现 tlv9062的针脚7在48V 幻象电源关闭时将出现峰值波形、如下面的黄色曲线所示。 TLV9062的引脚5 PIN6和 VDD 正常、不会出现未显示在波形中的压降。

4.与没有毛刷现象的正常情况相比,当48V 幻象电源关闭时,pin7引脚具有平方波而不是剧烈波。

5. TLV9062的有缺陷芯片由 EVM 板测试、发现工作正常。

您能否帮助分析这种现象的原因并提供解决方案?

此致

Wesley