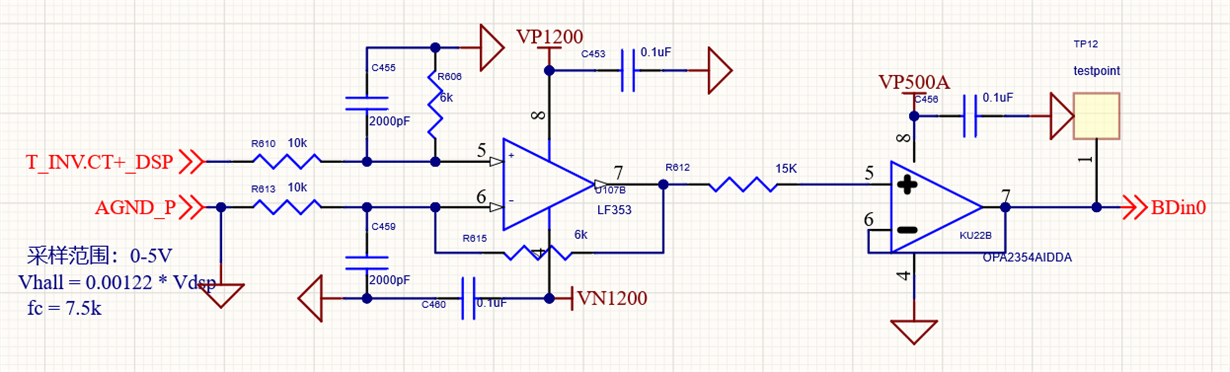

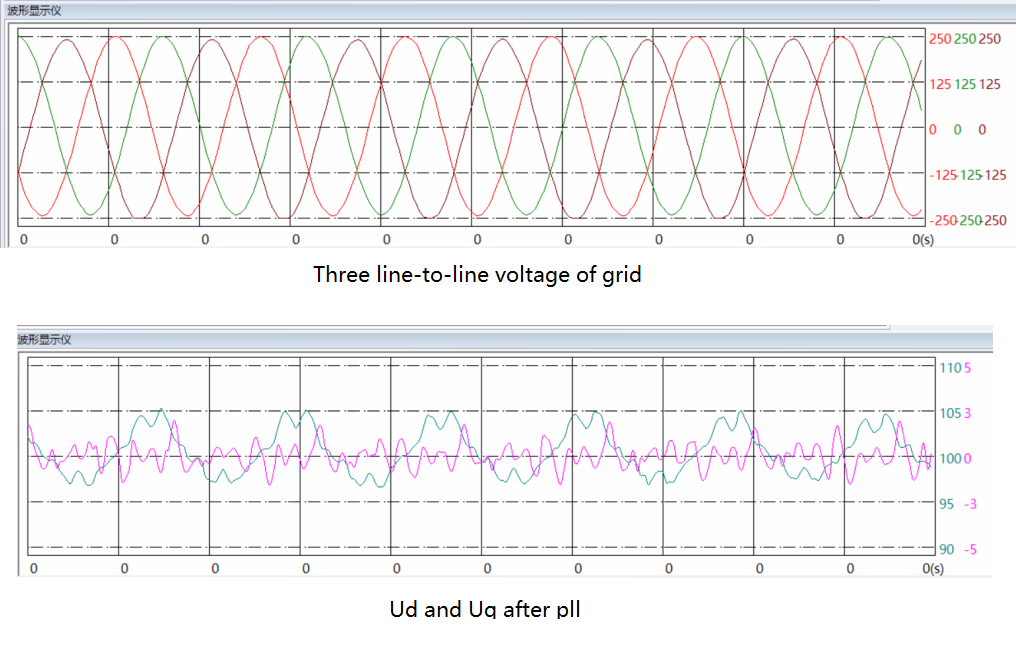

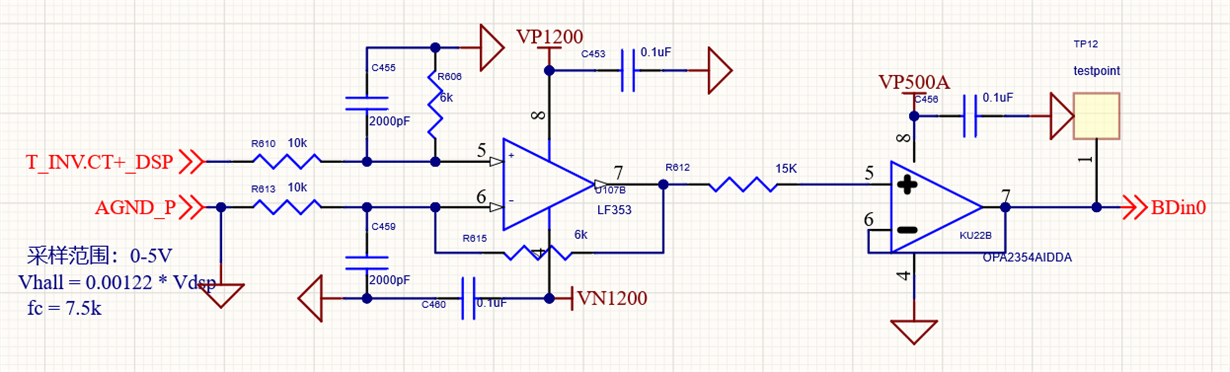

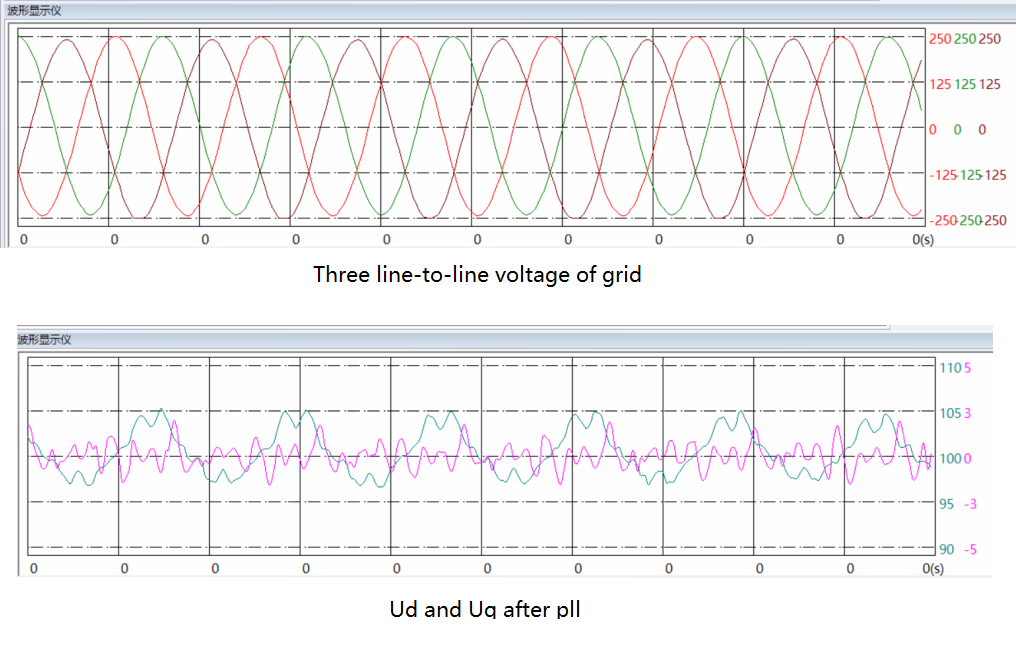

如下所示、我使用 LF253和 OPA2354AIDDA 来构建电压采样电路、该电路用于并网逆变器上的线间电压。 遗憾 的是、结果不能令人满意。BDin0端口连接到我的 DSP、AD 的输出如下图所示。 似乎三个线对线电压良好、 但 PLL 之后的 UD UQ 是坏的。

的是、结果不能令人满意。BDin0端口连接到我的 DSP、AD 的输出如下图所示。 似乎三个线对线电压良好、 但 PLL 之后的 UD UQ 是坏的。

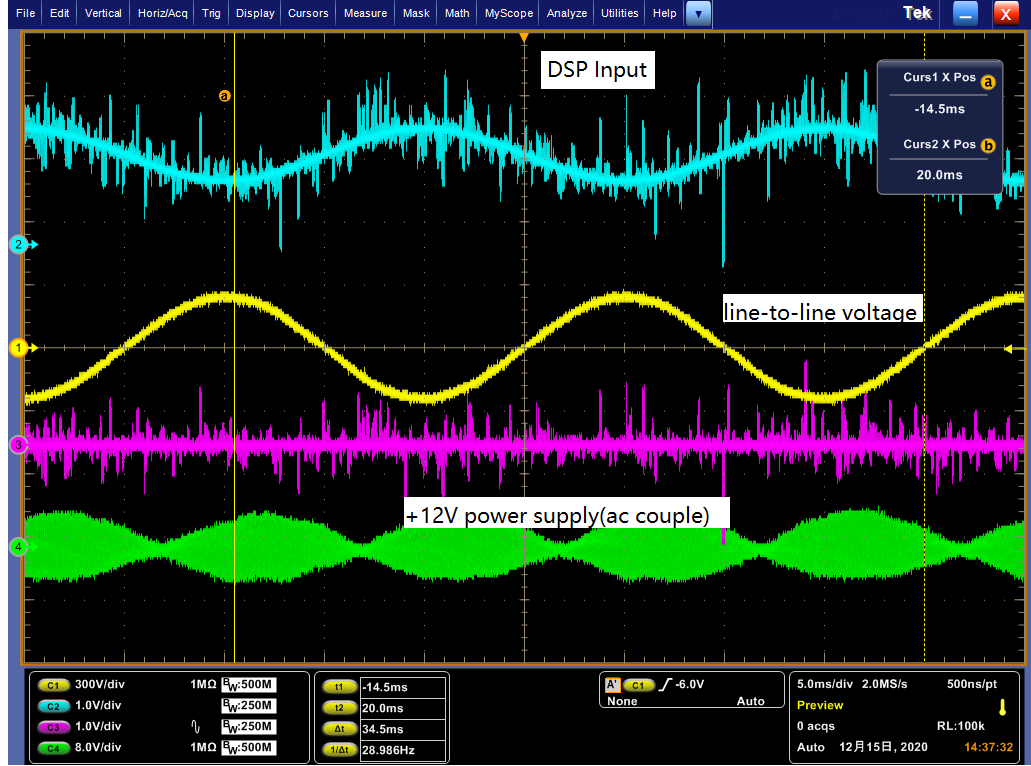

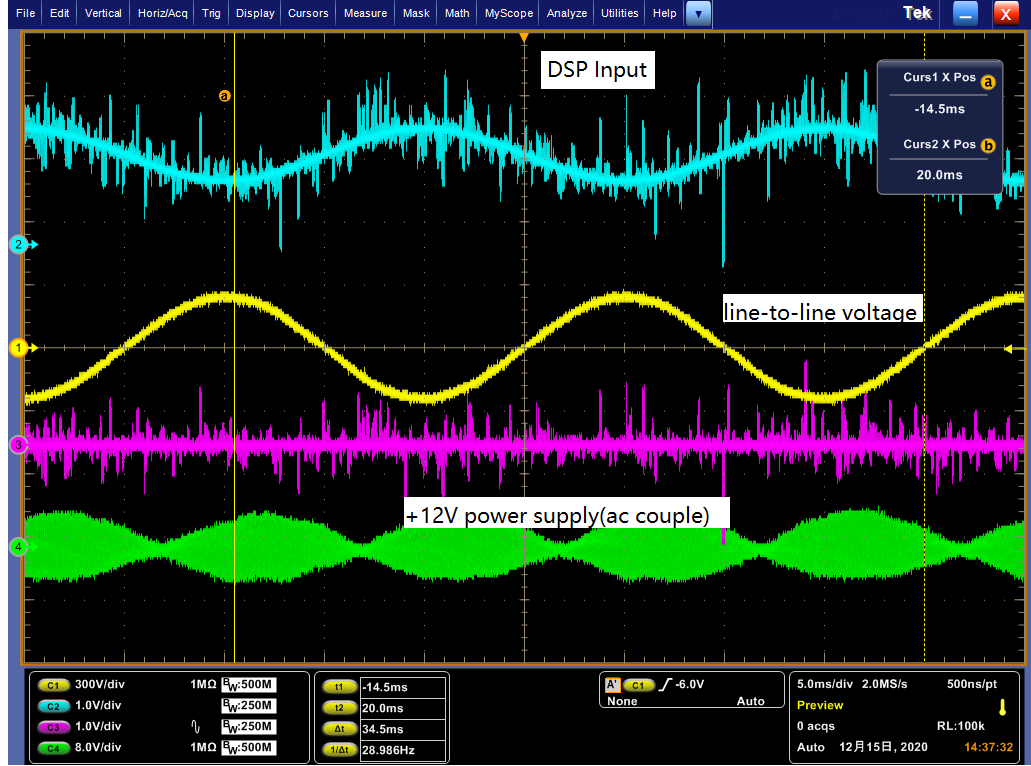

根据 示波器波形(如下所示)、LF353的电源具有严重的共模噪声、输出具有相同的噪声。 我想知道噪声是否会输入 DSP 并干扰 AD 采样结果、如果我需要将 LF353更改为另一个放大器。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

如下所示、我使用 LF253和 OPA2354AIDDA 来构建电压采样电路、该电路用于并网逆变器上的线间电压。 遗憾 的是、结果不能令人满意。BDin0端口连接到我的 DSP、AD 的输出如下图所示。 似乎三个线对线电压良好、 但 PLL 之后的 UD UQ 是坏的。

的是、结果不能令人满意。BDin0端口连接到我的 DSP、AD 的输出如下图所示。 似乎三个线对线电压良好、 但 PLL 之后的 UD UQ 是坏的。

根据 示波器波形(如下所示)、LF353的电源具有严重的共模噪声、输出具有相同的噪声。 我想知道噪声是否会输入 DSP 并干扰 AD 采样结果、如果我需要将 LF353更改为另一个放大器。

您好!

我不确定您的意思是"UD and Up After PLL (在 PLL 之后 UD 和 UP)"。。。 这是否不在所示的原理图中? 如果是、您能否指出原理图中的位置?

但是、从示波器图片中可以看到12V 电源的噪声(粉色)与 DSP 输入(蓝色)相关。 在布局中、电源和 DSP 输入是否彼此相邻(不是隔离式)? 我建议降低电源中的噪声、进而降低 DSP 输入中的噪声。

祝你一切顺利、

卡罗莱纳州

我会这样做:

为了实现最高的共模抑制(抑制两个信号接地端之间的噪声)、差分放大器的无源组件应紧密匹配。 最高的平衡会导致最高的共模抑制。 采用金属膜电阻器(薄膜电阻器!!!) 和 NP0电容。

e2e.ti.com/.../user_5F00_lf353.TSC

Kai