与此帖子相关的后续问题:

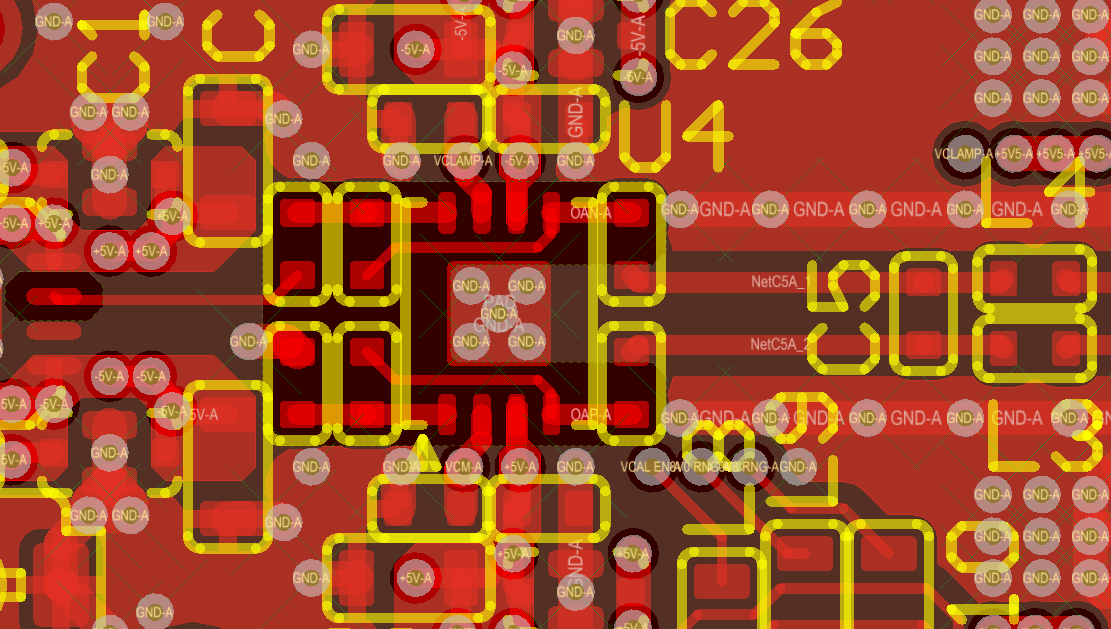

该板的层结构是什么? 我想知道第3层上的接地层在第2层反馈轨道下方的距离。

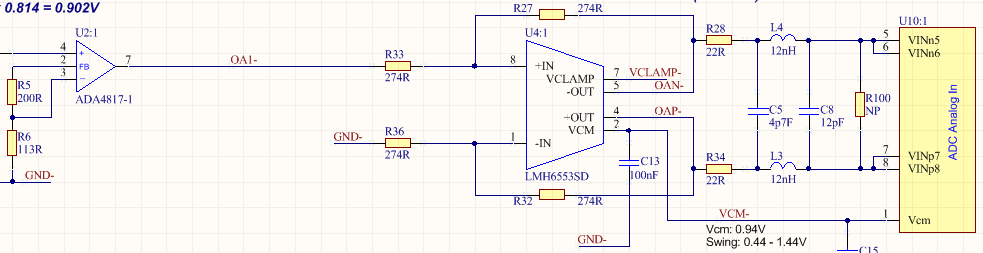

2.在 LMH6553SDEVAL SNOA528A 文档中、布局注意事项、第7项。 从器件下方和周围移除接地平面和电源平面、尤其是输入和输出

引脚。 但在布局上、输入和输出引脚下的第3层上有接地平面、因此应遵循哪种建议?

3.为什么移除 VCM 和 VCLAMP 引脚周围的接地平面? 这些电平通常不是直流电平吗?

我提出这些问题是因为我们看到 LMH6553布局存在一些带宽损耗、因此我们非常感谢您的帮助。

谢谢、Ken