主题中讨论的其他器件:LMV844、 OPA2171、 LMV842、 TINA-TI、 OPA4171

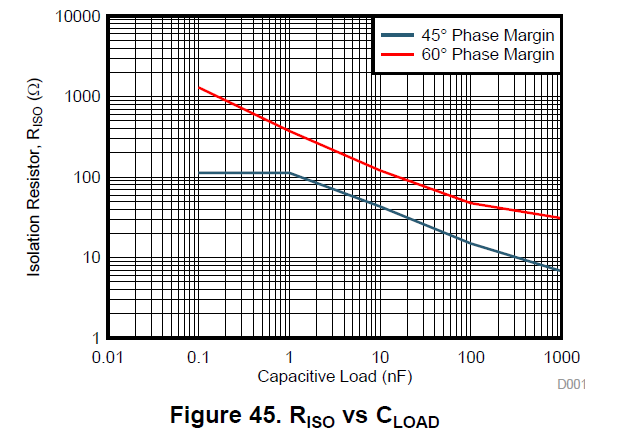

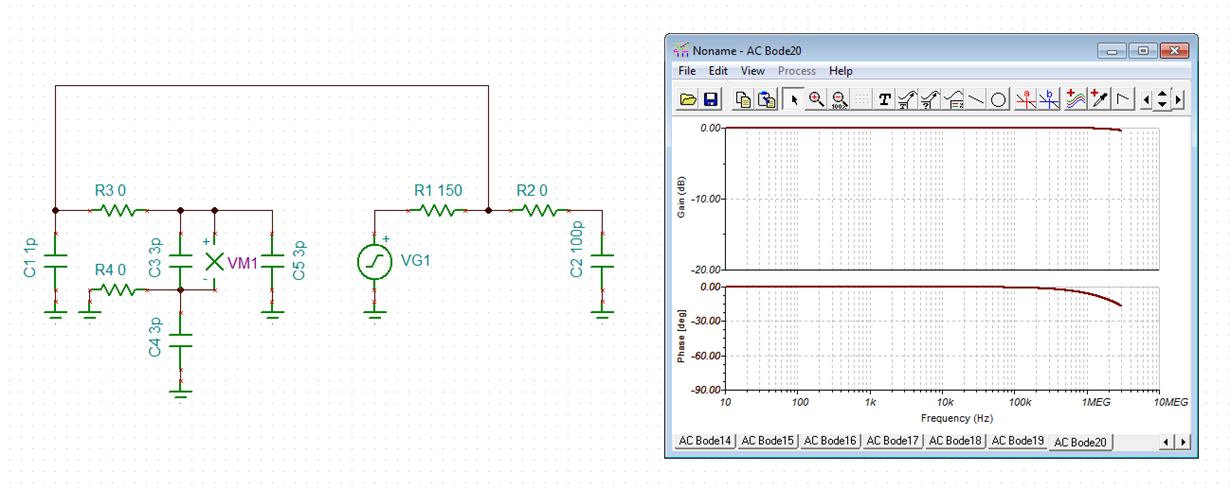

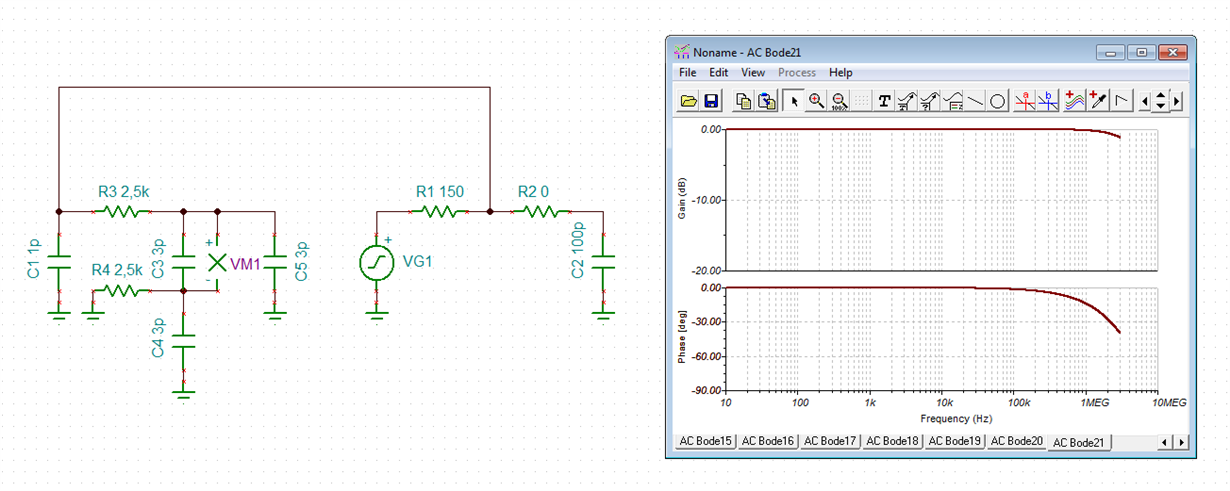

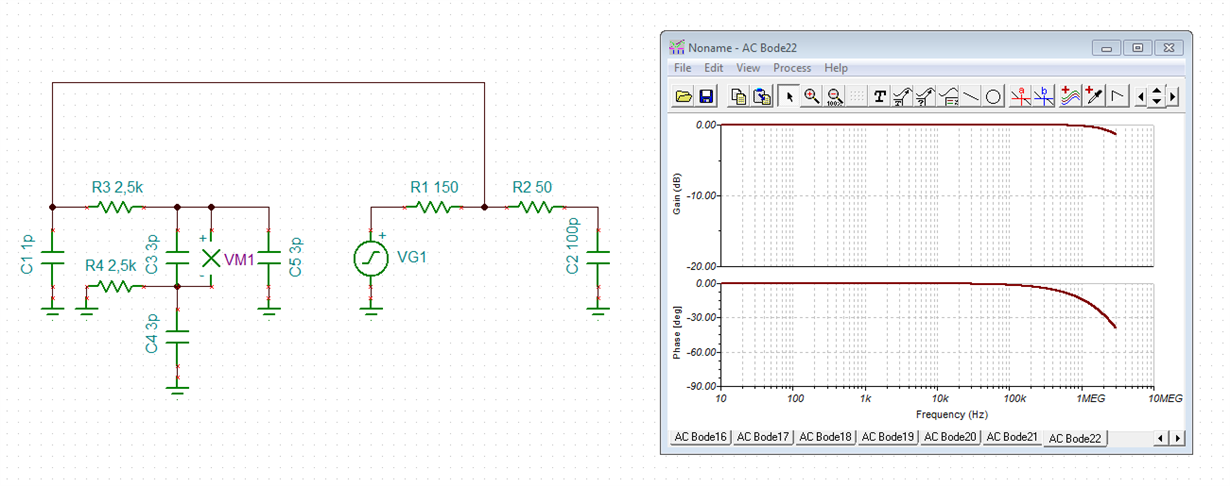

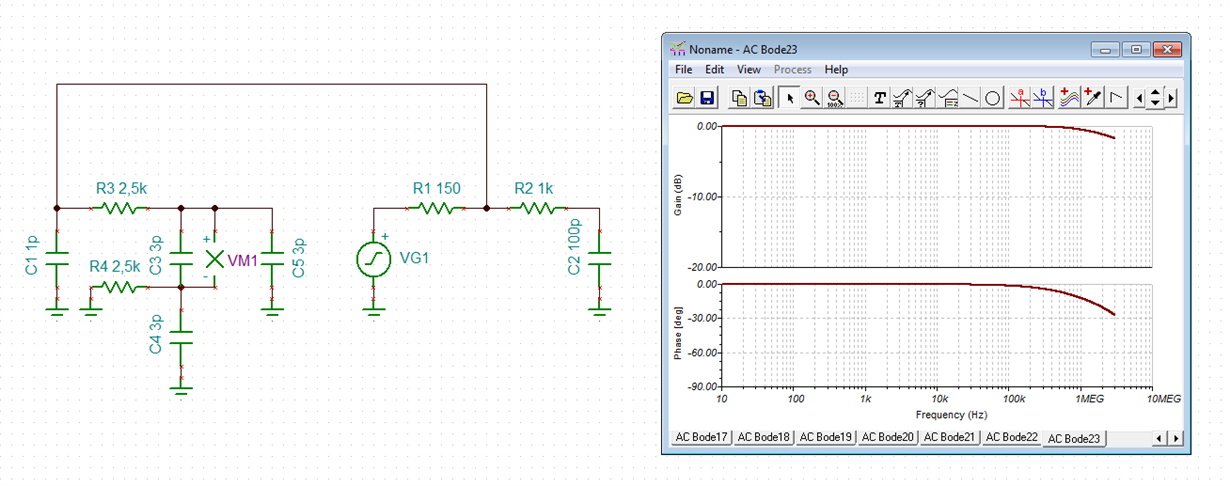

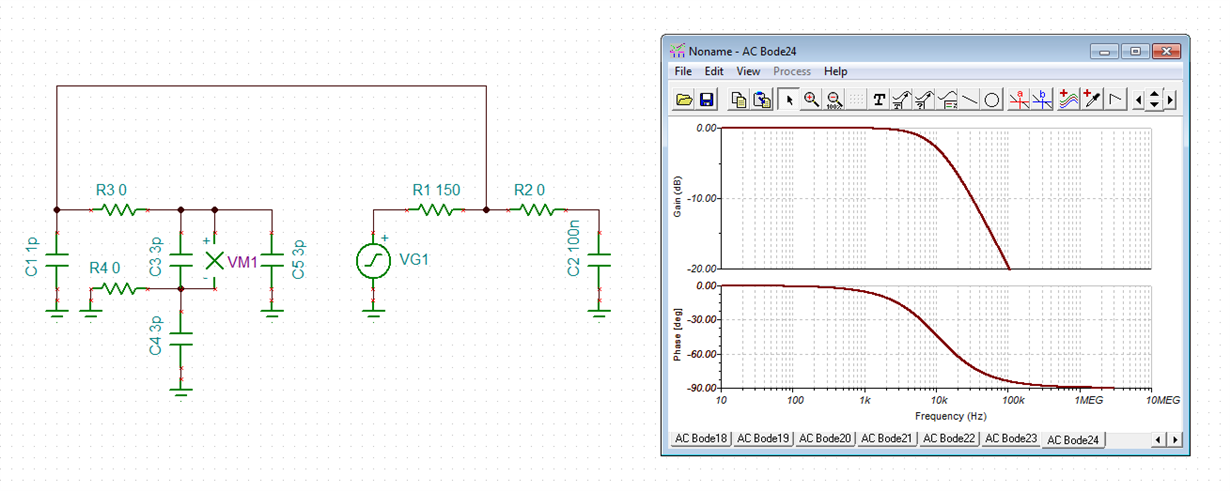

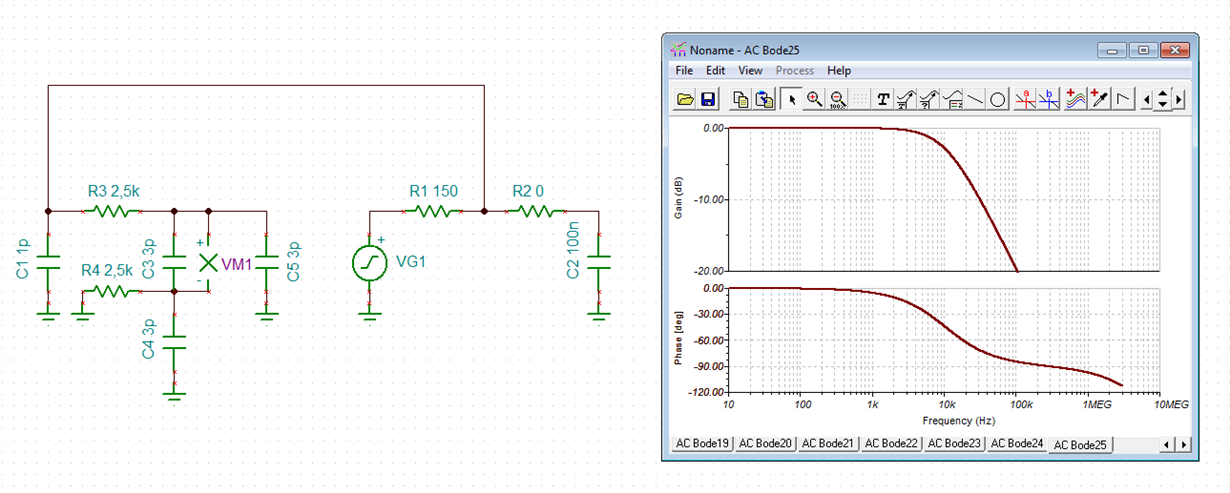

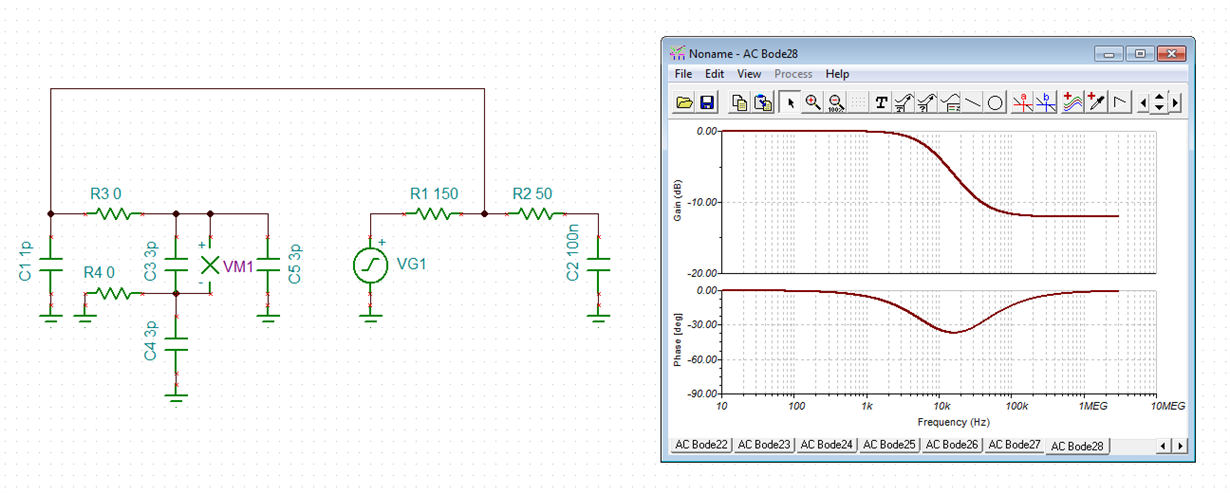

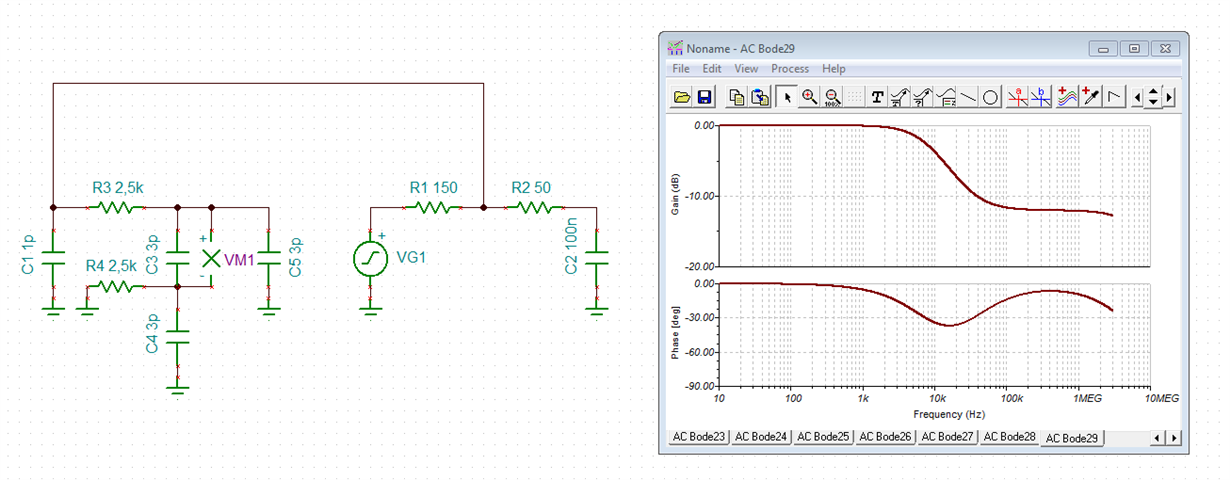

对于 OPA2171、您不仅提供了允许的最大 C_LOAD 和建议的 R_ISO 的图、还提供了45度和60度相位裕度的 R_ISO 与 C_LOAD 的图。 此图是否也适用于 LMV841/LMV842/LMV844?

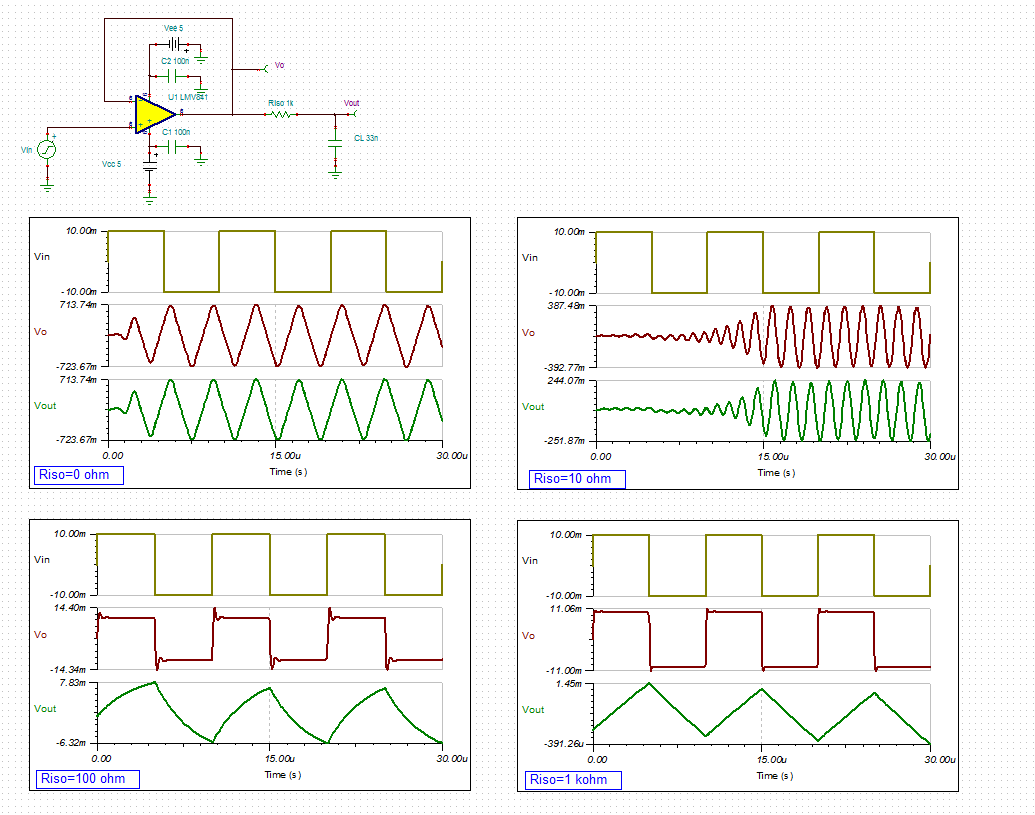

我始终至少有1k (2%)"R_ISO"、之后是最大33nF (可能为47nF)的电容器。 对我来说、风险很低。

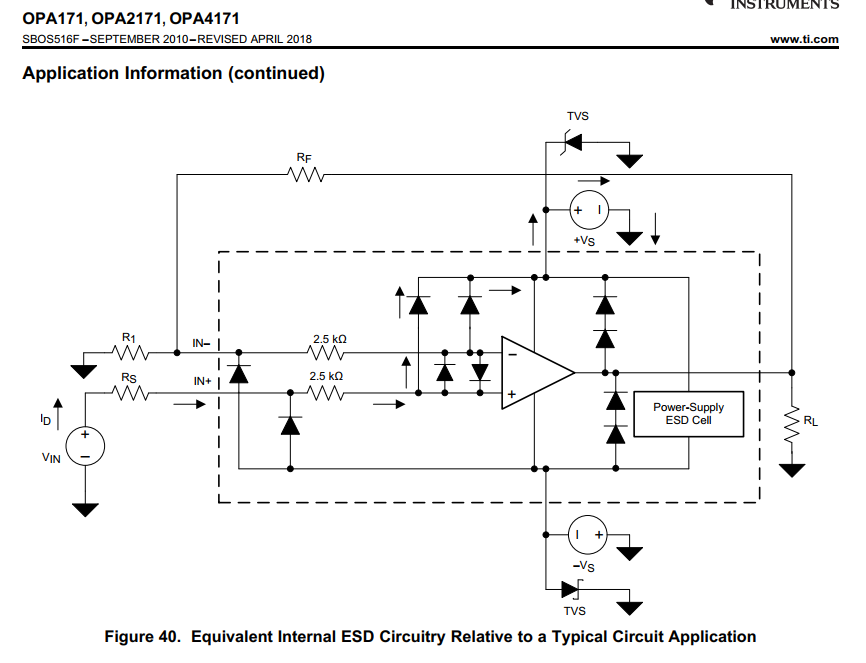

我可以通过查看 OPA2171图42尝试自己生成振幅图、但这不会提供相位数据、而且 OPA2171图42也存在一些差异、这让我感觉自己在数据表中没有可靠帮助的情况下: 我想图42是添加了 C_LOAD 影响的开环增益、但为什么峰值增益大于120dB 并保持在100Hz、而图19中的开环增益为130dB 至大约3Hz、而在100Hz 时仅为90dB?

(AN-1708标题听起来很有希望、但不包含附加价值。)