主题中讨论的其他器件: TL081

您好!

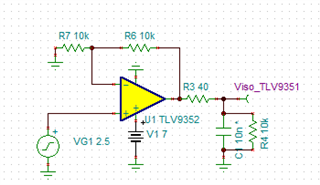

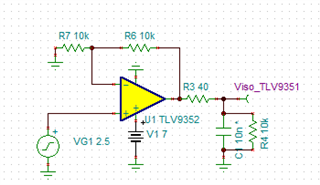

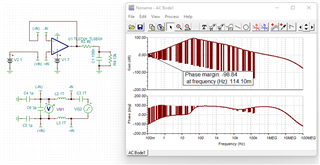

我正在使用 TLV9351通过 隔离电阻器驱动容性负载。 电路原理图已附。

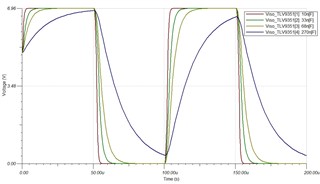

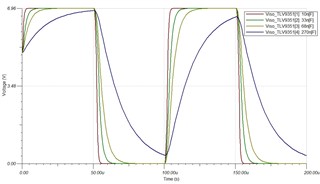

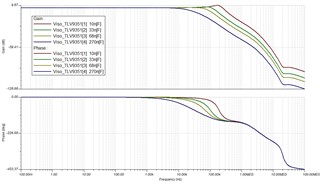

附加了仿真结果。

e2e.ti.com/.../Cload-Compensation_5F00_TLV9351_5F00_last.TSC

1.我可以使用的最大和最小容量是多少?

2.当电源电压为7V 时,如果我以0-7V 的输入电压驱动 TLV9351会发生什么情况? 我能像这样驱动它吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我正在使用 TLV9351通过 隔离电阻器驱动容性负载。 电路原理图已附。

附加了仿真结果。

e2e.ti.com/.../Cload-Compensation_5F00_TLV9351_5F00_last.TSC

1.我可以使用的最大和最小容量是多少?

2.当电源电压为7V 时,如果我以0-7V 的输入电压驱动 TLV9351会发生什么情况? 我能像这样驱动它吗?

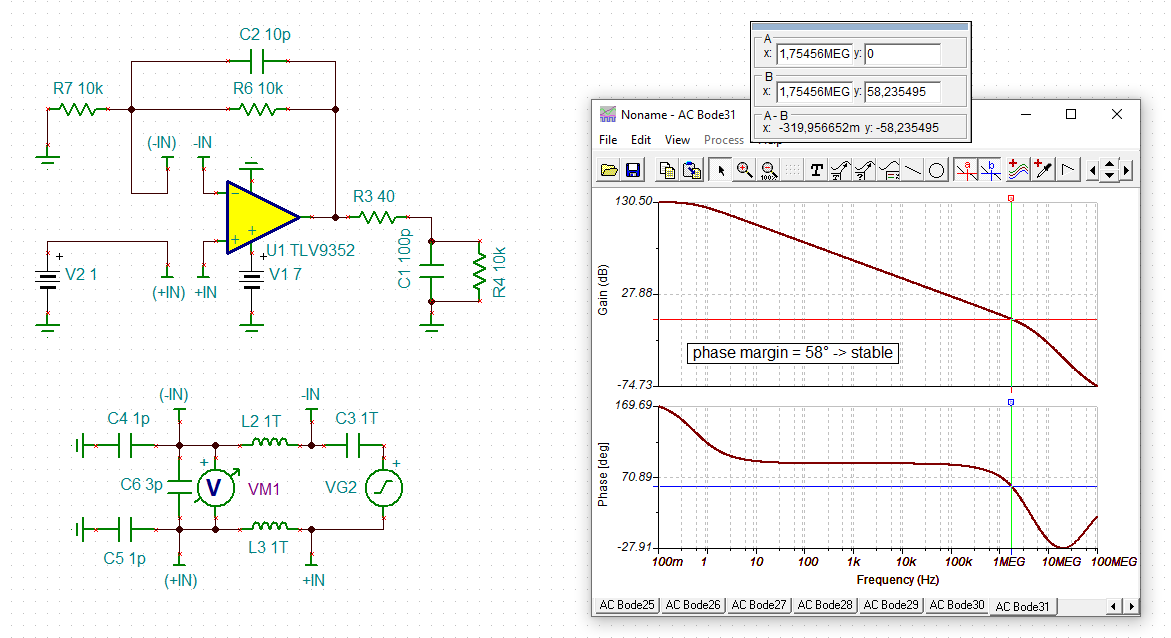

您好、Egemen、

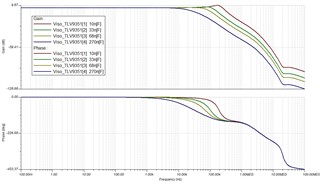

我会运行相位稳定性分析:

e2e.ti.com/.../egemen_5F00_tlv9352.TSC

请注意我为了增强稳定性而添加的相位超前电容 C2。

您可能还需要观看以下有关稳定性的 TI 培训视频:

https://training.ti.com/node/1138805

参考您的第二个问题:为了获得最佳性能、我会添加一个输入分压器、将输入电压限制在"更好"的输入电压范围(0V 到 Vs - 2V)、并防止输出级削波。

凯

Egemen、您好!

以下是之前提供的 Kai 培训系列的链接、网址为 https://www.ti.com/video/series/ti-precision-labs-op-amps.html

我不认为 Kai 的链接早点起作用、因为 TI 已经更改了视频登录页面。

设计的相位裕度很好地说明了电路的稳定性、过去、您希望确保至少40度的相位裕度、以应对器件的20度 PM (批次/晶圆制造)变化。

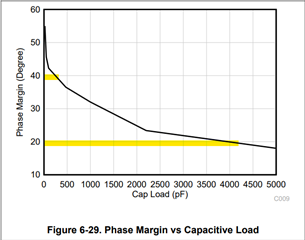

根据数据表中的图6-29、TLV935x 无需额外的电路即可驱动高达3500pF (3.5nF)的负载以提高稳定性。

有一些改善稳定性的方法、例如 RISO (R3)或添加反馈电容器(例如 Kai 的 C2建议)。

因此、为了回答您的问题、

在最终电路中、容性负载应在100nF 至220nF 之间、并附上仿真结果。

1.这个电路在这些电容下是否稳定?

2.增大电容也会增大相位裕度。

3.最小相位角应该是45度吗?

[/报价]1.由于74 & 83 >> 40度的相位裕度、该电路看起来是稳定的。

2.这是不正确的,通常增加电容会降低相位裕度。 RISO 和 RLoad 的选择会改变相补角。 我建议查看相关的培训、以充分确定您的补偿电路的大小。 此外、仿真显示的内容和器件在实际接收到的数据也会有所不同(因为 PM 是典型规格)。 因此、我建议对您的电路进行原型设计、以确保 RISO 是正确的值。

建议相位裕度至少为40度。

祝你一切顺利。

Carolina

您好!

我还设计了单位增益运算放大器(TL08XX)电路来驱动容性负载、但交流波特输出却很奇怪

这种设计有什么问题?