主题中讨论的其他器件:OPA365、 INA240

大家好、TI!

我构建了一个具有低侧电流感应功能且将 OPA365作为运算放大器的新电机控制器电路板。 运算放大器输出上会出现严重的振荡。 相位或栅极电压等所有其他波形看起来都很好、几乎没有振铃。

我想我知道它们的来龙去脉、但我不确定是否有什么我可以反对的地方、我想询问您对此有何想法或评论。

由于分流电阻器的电感和电源路径、我在高侧 FET 的漏极和低侧 FET 的源极之间添加了一个1uf 电容器、以抑制低侧 FET 源极上的初始电压脉冲。

该电容器降低了初始电压脉冲、但我认为它正与分流器和电源路径的电感形成一个 LC 电路、这会导致振荡。 您是否也认为这是原因、还是有我没想到的事情?

下面是我的意思:

但是、当我移除 HS-FET 漏极和 LS-FET 源极之间的电容器(在上图中、是黄色 C)时、在仿真和实际电路板上、振铃会显著降低。 另一方面、当我移除该电容器时、LS-FET 的源极上会出现较大的电压尖峰、这可能会损坏 DRV。 是否应考虑使用较低的电容? 目前其电容为1uF。

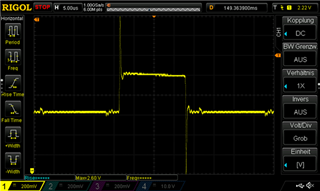

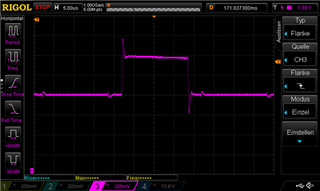

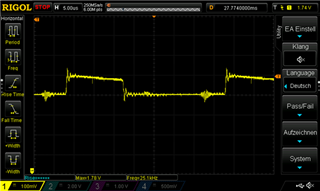

下面是测量电流时运算放大器输出的两张图、这张图中电流大约仅为4A:

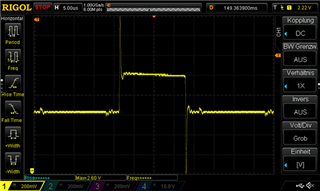

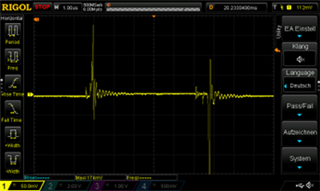

这是使用 Hs 漏极–LS 源极电容器时的情况:

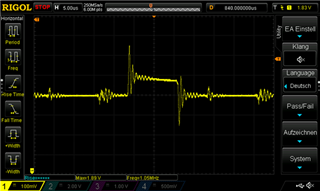

这不含 HS 漏极–LS 源极电容器:

这里是接地和 LS 源极之间电压的两张图:

这是使用 Hs 漏极–LS 源极电容器时的情况:

这不含 HS 漏极–LS 源极电容器:

例如、在大多数情况下、我对 INA240使用内联感测、但这不存在这个问题。 最好知道在这种情况下是否有一些事情可以提供帮助。 我无法更改分流器的电感、我已经使用了电感较低的分流器、我认为布局应该可以、底部有一些图片和所有原理图。

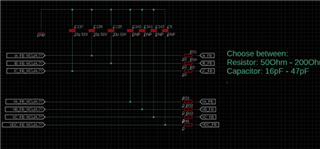

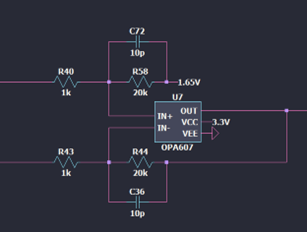

到目前为止、我已更改了运算放大器的输入滤波器、并且振荡减少了很多。

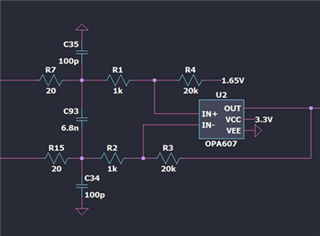

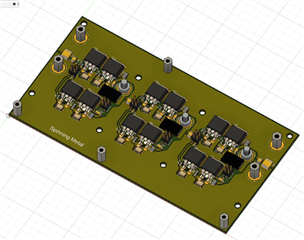

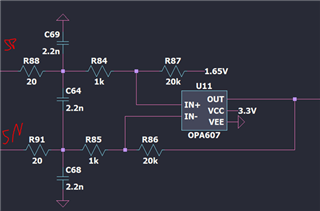

在我更换滤波器之前、您可以在下图中看到电路。 图片中的值是实值。

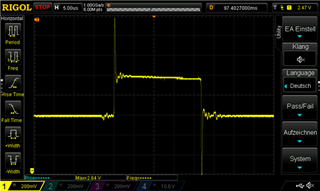

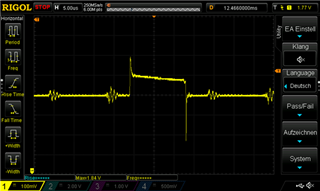

这是电路板上的运算放大器的输出:(如果不放置 C69和 C68、看起来会更糟)

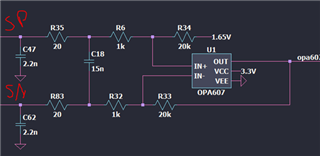

使用以下值、振铃大幅减少:

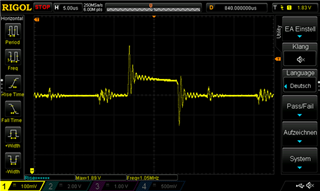

如此处所示:

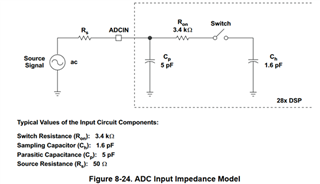

但是这会将截止频率降低到大约400kHz、我再也不会降低。 如何确定低侧电流感应中使用的运算放大器的最小带宽(对于内联、我很清楚)。 OPA365具有绝对足够的带宽。 我看到过很多经验公式、但取决于它真正依赖什么? 您是否有这方面的应用手册?

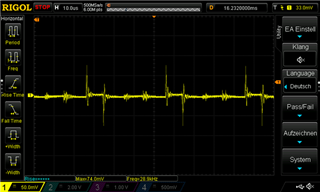

我所有三个相位的采样时间大约为150ns-500ns、具体取决于 MCU。 PWM 频率介于10kHz 和40kHz 之间。 占空的低侧 FET 的最短导通时间为最小值2-3us、通常为5us。 采样发生在 LS-FET 导通时间的中间、在这一点上、电压应该已经稳定到一个合理的值。

分流电阻器上的 di/dt 大约在30ns-40ns 内达到80A。 80A 是要测量的最大电流、运算放大器的输入端约为80mV (1m Ω 分流器、增益为20)。 这是 2V/us 的 dv/dt。

这种滤波器目前我还没有尝试、振铃可能较少、但我认为稳定时间会完全相同。

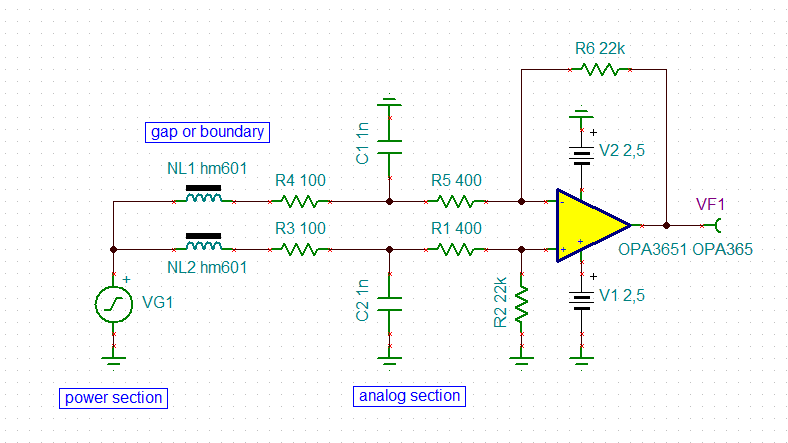

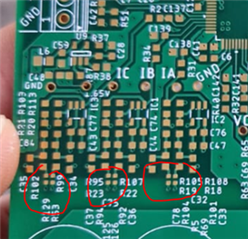

以下是布局和原理图:

运算放大器电路:

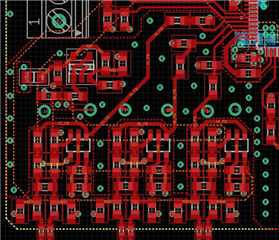

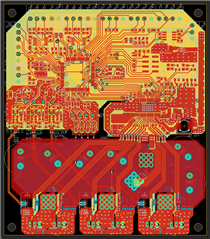

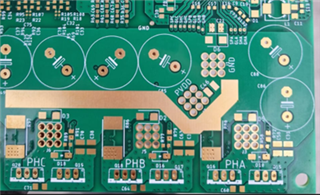

运算放大器布局:

感测迹线的布线:

此致、提前感谢您、

但以理