Other Parts Discussed in Thread: BUF802, TIOS101, UCC27517, BUF802RGTEVM

主题中讨论的其他器件: TIOS101、 UCC27517、

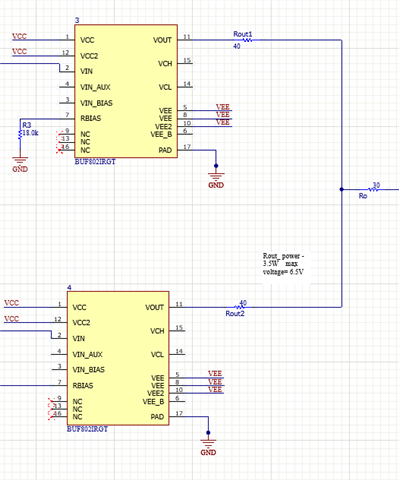

如下所示、我将两个 BUF802并行用作输出驱动器。

BUF802的输入是方波。

如何确定缓冲器向两个信号中添加了多大的传播延迟? 在数据表中找不到任何关于延迟的具体信息。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Debasmita 您好!

我相信您 针对该主题的回答已经提出了单独的问题/帖子。 如果您遇到某个客户帐户的高优先级项目问题、请提供有关所共享 BUF802子电路之外的客户电路/应用的时间表和详细信息。

似乎您并行使用两个 BUF802来提升缓冲器的驱动强度;客户担心其方波在500MHz 时的失真或信号传播不均匀。 客户是否执行了任何仿真或实验室电路板测试来展示是否需要研究 BUF802传播延迟?

如果可能、请详细说明客户需求和电路使用情况。 如果您愿意、您可以回复此主题、我可以关闭您提出的另一个有关器件间偏移的问题:

此致!

亚历克

Debasmita 您好!

您的客户是否在其信号链上遇到过失真或信号损失? 如果它们具有性能的品质因数或数字目标、我可以在实验中使用奇异 BUF802RGTEVM 来检查500MHz 下的传播延迟。

您能否分享以下详细信息?

-原理图中的 VCC 和 VEE

-电压电平以及您在方波500MHz 输入上拥有的任何其他细节,如占空比

-说明6.5V 电压是否是 Rout2的测量/仿真输出电压,其中 Rout2_power = 3.5mW。

-客户的绩效目标是什么? 它们是否具有可接受的延迟量? 可接受的失真量?

通常、由于 BUF802是具有零反馈路径的开环缓冲器、因此传播延迟仅是输入信号通过晶体管网络到达输出所需的时间。 使用3.1GHz 的增益带宽积、可以公平地保证 BUF802不会成为信号链总传播延迟的限制/慢因素。

分享详细信息后、我可以提供更好的想法、如果需要进行测量、我会进入实验室。 但是、如果我没有要查找的目标值或首选值、我将无法在实验中进行测量。 正如您的客户所说、Clemens 先前提出的 UCC27517的上升时间和下降时间过长。 请协助提供我所要求的信息。

感谢你能抽出时间。

此致!

亚历克

Debasmita 您好!

感谢您提供更多信息和分享 EVM 测试的结果。 如果关键规格是缓冲器之间的延迟、并且 EVM 测试的传播延迟是可以接受的、那么我同意 ALEC 的观点、即导致这一问题的主要因素将是布线/电路板设置对称性而不是缓冲器。

如果 BUF802在线性区域内工作(在数据表中列出的推荐规格范围内)、那么该器件将不会影响在几纳秒内测得的延迟。 下面是测量数据、显示输入/输出遵循几 ps 之内、远低于测量的1.6ns 信号链:

谢谢!

西马