Other Parts Discussed in Thread: OPA2990, LM358, DAC0808

主题中讨论的其他器件:OPA2990、、 DAC0808

大家好、

有关问题说明、请参阅以下链接。

DAC0808:DAC 工作问题-数据转换器论坛-数据转换器- TI E2E 支持论坛

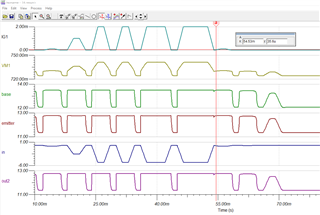

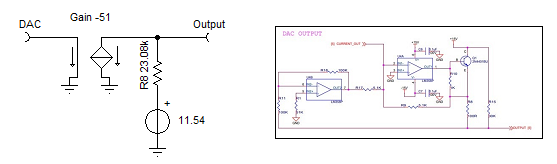

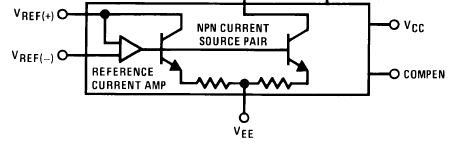

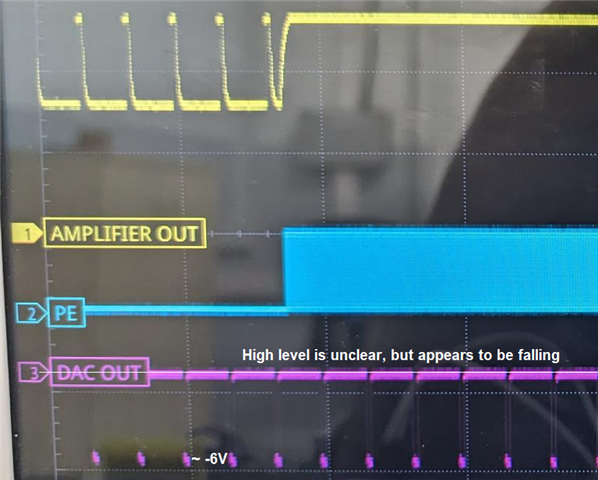

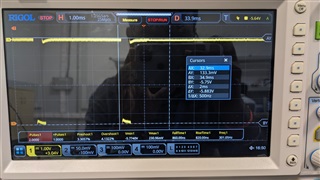

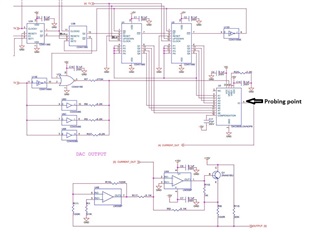

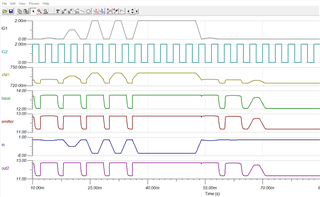

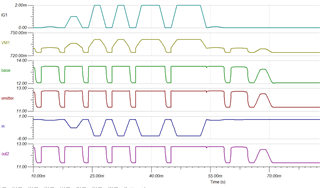

当我们将所有1馈送到 DAC 输入时、我们已在 U5.4处捕获了图像。 DAC 输出的振幅几乎没有差异。 它是否会在放大器输出端导致此问题?  旧版电路板

旧版电路板

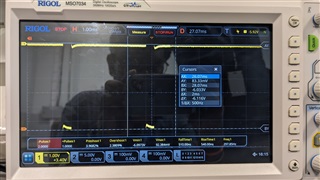

---新董事会

---新董事会

此致、

斯里坎特·卡丘

-->金板

-->金板  -->新电路板

-->新电路板

-->旧电路板

-->旧电路板  -->新电路板

-->新电路板

-->旧电路板箱

-->旧电路板箱  -->新电路板案例

-->新电路板案例  -->旧电路板

-->旧电路板  -->新电路板

-->新电路板