Other Parts Discussed in Thread: OPA2994

Thread 中讨论的其他器件:OPA2994

工具与软件:

你(们)好

根据图5-49短路电流与温度间的关系、 该曲线是否意味着用户可以持续将输出端短接至 GND?

我的应用条件如下

封装:8引脚 SOIC

V+= 6V

V-= GND

仅使用通道1且 OUT1 = GND

是否处于安全状态?

谢谢

此致

本

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Carolina

此应用主要是为了限制功率以避免 Q1永久损坏

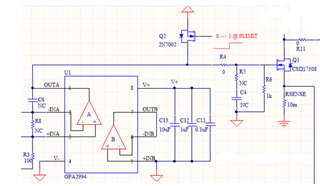

在流经 Q1的电流期间触发目标电源后、我们需要关闭 O1 (将 MOSFET 的栅极驱动为0)。

由于 OPA2994没有用于关断该器件的 EN 引脚、因此我们改用电源切断(事件触发器将 V+与电源断开)。

验证后、我们发现 V+必须放电一段时间、该时间内也允许电流通过、

Q1仍然存在风险

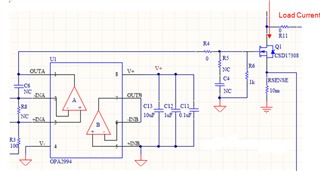

我们正在计划增加一个 Q2、将栅极拉至 GND、这相当于将 OPA2994的 OUTA 短接至 GND、

但我们不确定可行性是否可以

其中:V+=6V,V- =GND

欢迎您的评论!

谢谢

此致

本

您好、Carolina

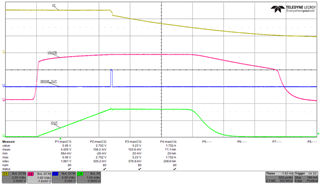

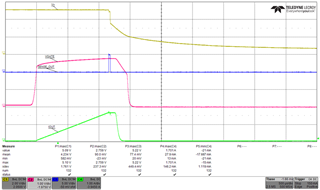

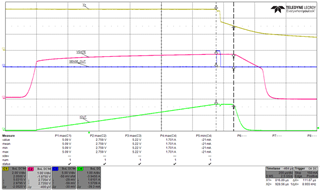

移除 C13有助于缩短放电时间、生成的波形如下。

根据、应用电路仍然是问题

1、放电时间不能控制在期望值以下,通道元件的放电电阻只规定典型值

2.如果负载电流斜升更快、我们认为放电时间将成为关闭 MOSFET 的主要时间

因此、OPA2994的短输出至 GND 似乎是必需的选项

我将给定热阻的最大功率耗散简单估算为 θ JA

PDMAX (W)=(150 -25)/170 = 0.735

PD @ SC (W)= V+ x ISC = 5 x 0.085 = 0.425

PD @ SC < PDMAX (正常运行)

在 V+放电期间、功率耗散也会降低。

欢迎您提出任何意见和建议!

谢谢

此致

本