主题中讨论的其他器件:DS90LV011A、、、 TINA-TI

工具与软件:

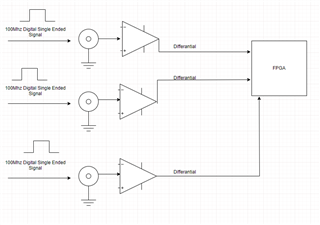

我想比较来自三个不同来源的单端信号的上升沿。 信号的频率约为100 MHz。 我想使用 FPGA 比较这些来源的数据。 由于 FPGA 和 SMA 连接器在 PCB 上的物理位置将彼此远离、因此我打算将信号转换为 PCB 上的差分信号、并以这种方式布线。 下面是方框图。

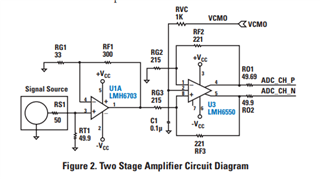

在研究这个主题时、我看到了 TI 的高性能模拟前端应用手册。

但是、我有几个问题、非常感谢您对这些问题的帮助:

- 该电路是否是此应用的最佳选择?

- 怎样才能防止噪声影响100 MHz 输入信号?