Thread 中讨论的其他器件: Tina-TI、 JFE150、 Strike

工具与软件:

您好!

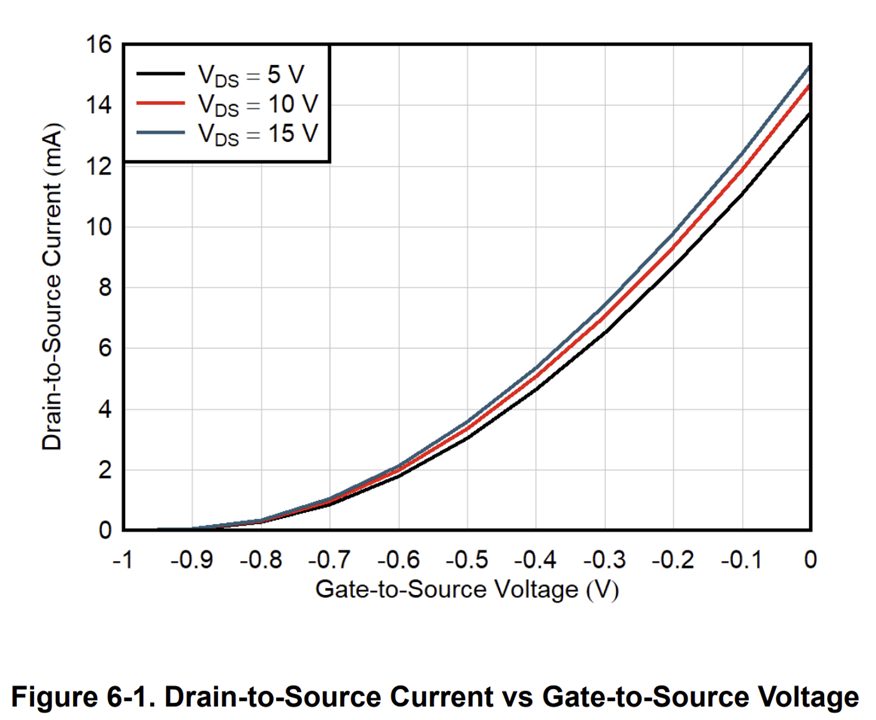

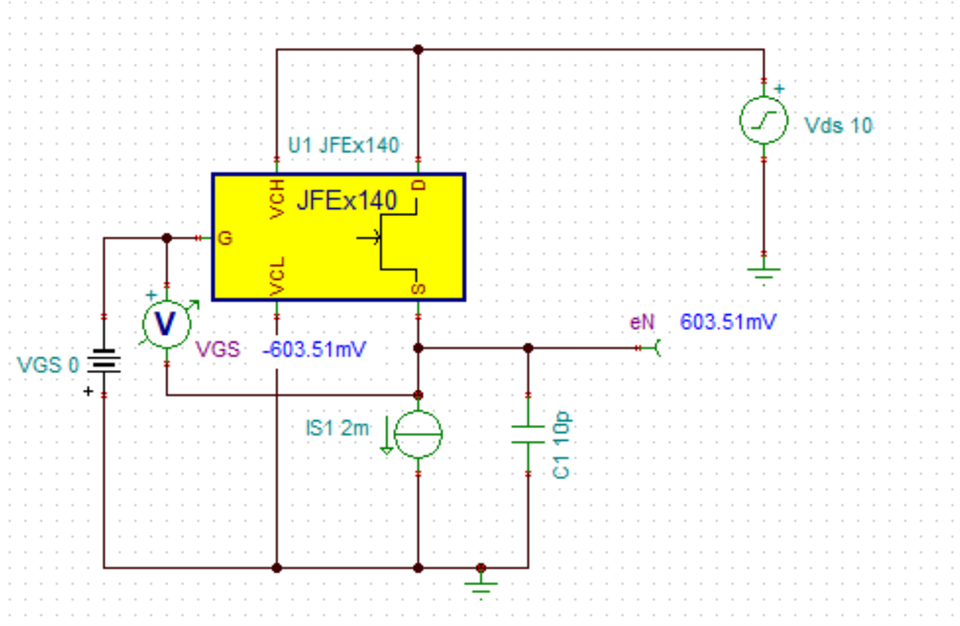

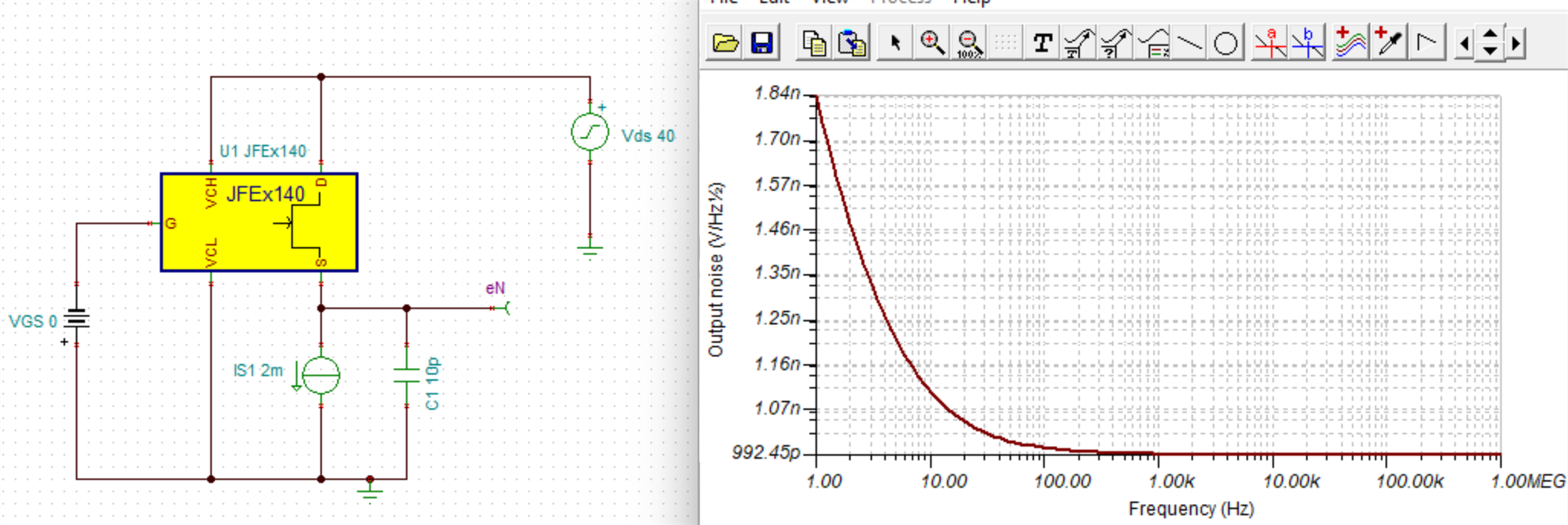

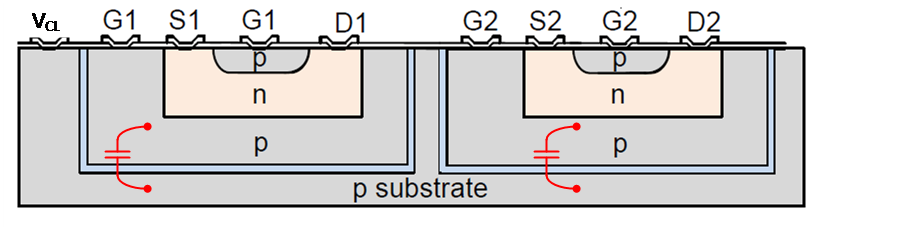

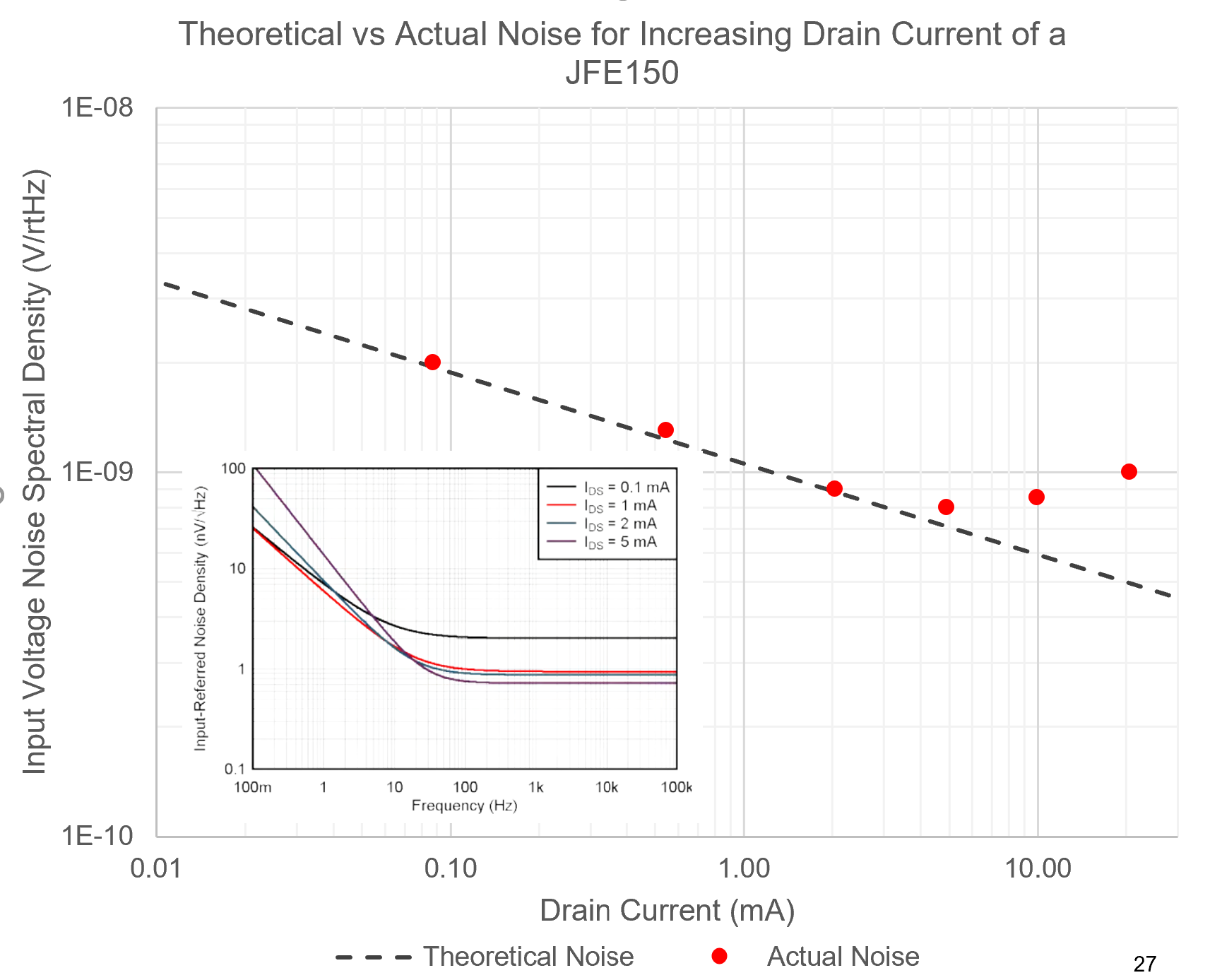

我们目前正在评估 JFE2140、并注意到 Spice-Model 和实际电容(栅极到源极和栅极到漏极)之间存在相对较大的差异、这会在我们的应用中导致很多额外的噪声。

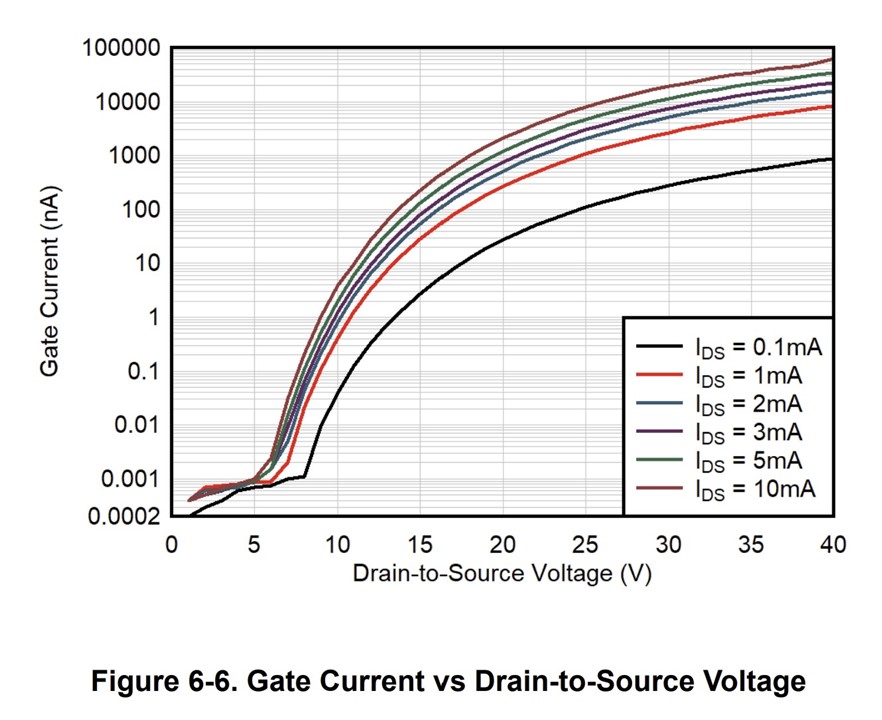

数据表列出了图6-17中的一些电容、但遗憾的是、未注意测量这些测量 是在哪个栅极电压下进行的。 使用 E4980A 测量容量时、图6-17似乎给出了栅源电压约大于0.7V 的容量。

是否有更具体的数据表明在更广泛的栅极电压范围内具有不同的容量? Spice 模型(在 LTspice 中使用 PSpice 参数)讲述了一个完全不同的情况、一个需要大约5 pF 的额外栅极漏极、另一个10 pF 栅极源极来符合我们在现实世界中看到的结果。

有人可以确认这些更高的容量和 Spice 模型的误导行为吗?

此致、

Gerrit