主题中讨论的其他器件:ADC128S102、 、OPA4991-TLV2374-TLV9004 、EP、EP、 、 OPA4991、 OPA4H199-SEP

工具与软件:

你好。

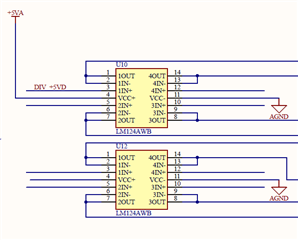

我将运算放大器 LM124A 部署为电压跟随器、旨在通过 SAR 12位 ADC ADC128S102监控每个电源并通过 SPI 通信将其提供给 MCU。 当我完成实际制造并测量了5VD 时、我发现从 OPAMP 输出到 ADC 输入之间存在大约1.5V 的压降。 (3.985V、3.834V)我为您发送以下电路图的摘录。

您认为有什么因素会导致压降?

此外、我们还想知道如何最大限度地减小电路设计中的压降。

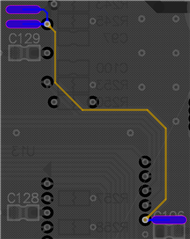

PCB 设计为0.181mm。

我很感谢您的答复。

此致、

郑承宪