Other Parts Discussed in Thread: TLV1842-Q1, TLV1832-Q1

主题中讨论的其他器件: TLV1832-Q1

工具与软件:

尊敬的 TI 支持部门:

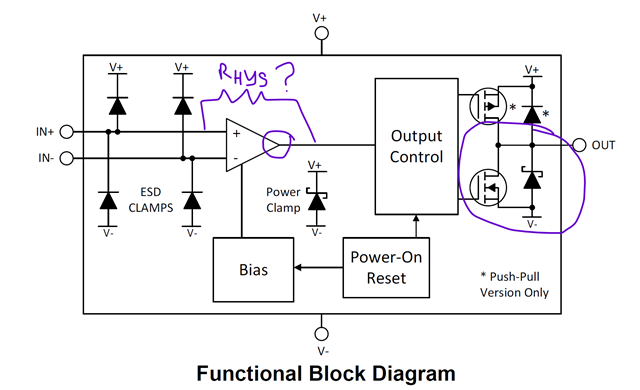

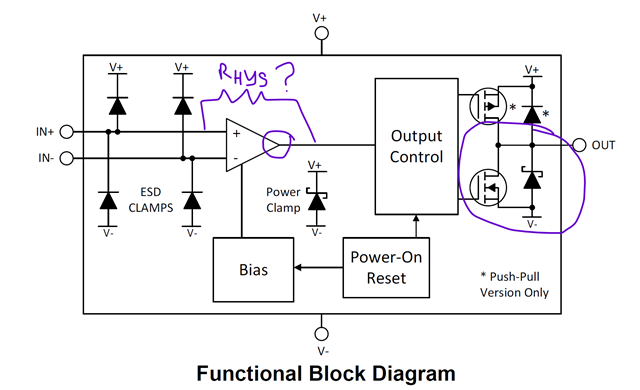

我将查看 TLV1842-Q1的数据表、并想为电路添加迟滞。 从芯片连接迟滞电阻器(如下所示)是否正确、考虑方框图显示输出端有一个开漏?

此致

ENA

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TLV1842-Q1, TLV1832-Q1

工具与软件:

尊敬的 TI 支持部门:

我将查看 TLV1842-Q1的数据表、并想为电路添加迟滞。 从芯片连接迟滞电阻器(如下所示)是否正确、考虑方框图显示输出端有一个开漏?

此致

ENA

尊敬的 Ena:

无法物理连接以紫色绘制的反馈电阻、因为您无法访问器件的内部节点。 您只能访问引脚、因此反馈电阻器会从 OUT 连接到 IN+。

我对这个问题有点困惑。 正如 Clemens 所说、迟滞的总体行为将取决于上拉电阻器值、因为 TLV1842-Q1是开漏器件。

这些资源展示了通过电阻反馈网络设计外部迟滞的过程。 对于这两本指导手册、我们使用了开漏器件、因此您可以了解上拉电阻器将如何影响迟滞行为:

尊敬的 Ena:

请参阅 具有迟滞功能的同相比较器电路。 您的连接正确、因为您需要通过反馈电阻器连接到 IN+。 输入源 Vin 需要通过电阻器连接到比较器的 IN+、因为它是低阻抗源。 您希望 IN+是一个求和节点、因为电压是 Vin 与 Rhys 连接的迟滞之和。