器件型号:LP-MSPM0G3519

工具与软件:

大家好、团队成员:

我有 TI 提供的示例案例、其中读取/写入0x00001000地址。

现在想要尝试编程并从0x41E00000区域读取。

使用 SDK 中的可用功能尝试将其更改为从0x41E00000开始进行写入时、我无法进行写入。

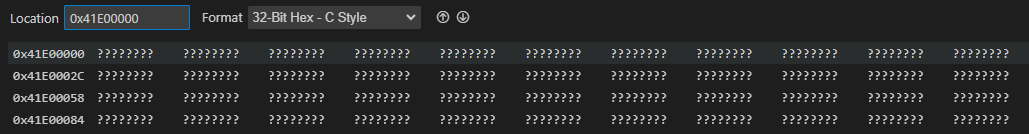

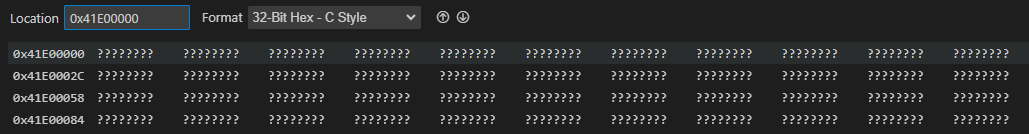

内存显示"??" 在 CCS 的 MEMORY 视图中、如何使用该存储器进行写入和读取操作?

请支持人员解决此问题

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号:LP-MSPM0G3519

工具与软件:

大家好、团队成员:

我有 TI 提供的示例案例、其中读取/写入0x00001000地址。

现在想要尝试编程并从0x41E00000区域读取。

使用 SDK 中的可用功能尝试将其更改为从0x41E00000开始进行写入时、我无法进行写入。

内存显示"??" 在 CCS 的 MEMORY 视图中、如何使用该存储器进行写入和读取操作?

请支持人员解决此问题

谢谢。

尊敬的 Eswaran:

编译器不会使用当前 SysConfig 生成的链接器将存储器位置0x41E00000识别为有效的存储器位置。

您需要调整链接器文件(.cmd)。 目前在 SysConfig 生成的版本中、其数据存储器部分将从0x41D00000开始。

此致、

Luke

/***************************************************************************** Copyright (C) 2023 Texas Instruments Incorporated - http://www.ti.com/ Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met: Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution. Neither the name of Texas Instruments Incorporated nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission. THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. *****************************************************************************/ -uinterruptVectors --stack_size=256 /* * Note: SRAM on this device is continuous memory but partitioned in the * linker into two separate sections. This is to account for the upper 64kB * of SRAM being wiped out upon the device entering any low-power mode * stronger than SLEEP. Thus, it is up to the end-user to enable SRAM_BANK1 for * applications where the memory is considered lost outside of RUN and SLEEP Modes. */ MEMORY { FLASH (RX) : origin = 0x00000000, length = 0x00080000 SRAM_BANK0 (RWX) : origin = 0x20200000, length = 0x00010000 SRAM_BANK1 (RWX) : origin = 0x20210000, length = 0x00010000 BCR_CONFIG (R) : origin = 0x41C00000, length = 0x000000FF BSL_CONFIG (R) : origin = 0x41C00100, length = 0x00000080 DATA (R) : origin = 0x41E00000, length = 0x00004000 } SECTIONS { .intvecs: > 0x00000000 .text : palign(8) {} > FLASH .const : palign(8) {} > FLASH .cinit : palign(8) {} > FLASH .pinit : palign(8) {} > FLASH .rodata : palign(8) {} > FLASH .ARM.exidx : palign(8) {} > FLASH .init_array : palign(8) {} > FLASH .binit : palign(8) {} > FLASH .TI.ramfunc : load = FLASH, palign(8), run=SRAM_BANK0, table(BINIT) .vtable : > SRAM_BANK0 .args : > SRAM_BANK0 .data : > SRAM_BANK0 .bss : > SRAM_BANK0 .sysmem : > SRAM_BANK0 .TrimTable : > SRAM_BANK0 .stack : > SRAM_BANK0 (HIGH) .eeprom_bss : palign(8) {} > SRAM_BANK1 .eeprom_data : palign(8) {} > SRAM_BANK1 .BCRConfig : {} > BCR_CONFIG .BSLConfig : {} > BSL_CONFIG .DataBank : {} > DATA }

尊敬的 Luke:

感谢您的答复。 通过建议的更改、我仍然面临同样的问题。 请验证我所做的操作是否正确。

谢谢!

Estwar G.

尊敬的 Eswar:

我正在研究这个问题,我也不能让它在我的最后工作 ECC 区域 0x41D00000正常工作、但未校验区域的擦除失败。 我需要对此进行调查。

您是否能够将 ECC 区域与 ECCGenerated 函数一起使用?

尊敬的 Luke:

感谢您的确认、也感谢您对该问题的调查。

是的、我已经尝试使用0x41D00000 ECC 区域、但一次仅写入64位时成功。

尝试使用32位函数时、我的第一次写入成功、但当尝试在0x41D00004写入下一个4字节时、该值会在0x41D00000被覆盖。 这种情况发生在整个1KB 扇区中。 -仍然有一个问题无法解决。

我还没有尝试过的其他两个函数。 将尝试检查并告知您。 谢谢。