主题中讨论的其他器件:MSPM0L1306

工具与软件:

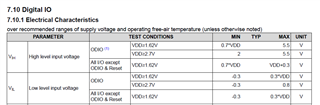

在测试5V ODIO 引脚的数字输入逻辑时、我发现当 VDD 为3.3V 时、电压降低~1.5V 时、输入引脚出现低电平。 根据下面显示的数据表、我预计它会更接近0.8V。 这是一个已知问题还是缺少某种配置?

我已经尝试过使用内部下拉电阻器(接通和断开)进行调试。 迟滞打开和关闭。 测试了 RGE 封装 PA1输入。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

在测试5V ODIO 引脚的数字输入逻辑时、我发现当 VDD 为3.3V 时、电压降低~1.5V 时、输入引脚出现低电平。 根据下面显示的数据表、我预计它会更接近0.8V。 这是一个已知问题还是缺少某种配置?

我已经尝试过使用内部下拉电阻器(接通和断开)进行调试。 迟滞打开和关闭。 测试了 RGE 封装 PA1输入。

您好、Diego:

这是对应用板的一个非常简单的测试、但我明天将对 EVM 进行仔细检查、以排除我的设计有任何异常之处。 更像是完整性检查。

我的设置是将4.7k Ω 连接到直流电源。 我上下改变了电压。 当将电压降低到1.5V 以下(在处理器引脚上进行测量)时、处理器开始寄存低电平。 根据我的理解、当开漏 IO (ODIO)的 VDD 高于2.7V 时、数据表上开始出现低电平的最大电压为0.8V。 我的目标是弄清为什么数据表和处理器之间存在差异、以及我可以做些什么。

在此测试中、应该不需要上拉电阻器(甚至下拉电阻器)。 我只是尝试了几个条件,因为我拔出我的头发一点点,以找出发生了什么。

Diego,

我使用软件轮询示例和 MSPM0L1306 EVM 进行了检查、PA1寄存器为0的电压经测量为1.65V。

自从今天考虑它之后、我认为我可能更好地理解了数据表。 数据表规定 ODIO 寄存零的最大电压(VIL)为0.8V。 我最初的解释是转换电压将为0.8V。 正确的解释可能是、在高电平输入电压(VIH)电平未定义之前、保证零的最大电压为0.8V 或任何更高的电压、它可能是0或1。

这种理解是否正确?