主题:SysConfig 中讨论的其他器件

工具/软件:

尊敬的团队:

我的客户在通过 SysConfig 配置防火墙时遇到问题。

- 当他们尝试为 L2OCRAM BANK4 SLV 和 L2OCRAM BANK5 SLV 设置防火墙时、HsmClient_setFirewall()返回 SystemP_FAILURE。 此外、还会在 UART 上收到一条错误消息"[HSM_CLIENT] Set Firewall Request Nacked by HSM server"。 是否无法在 L2OCRAM 的这两个存储体上设置防火墙?

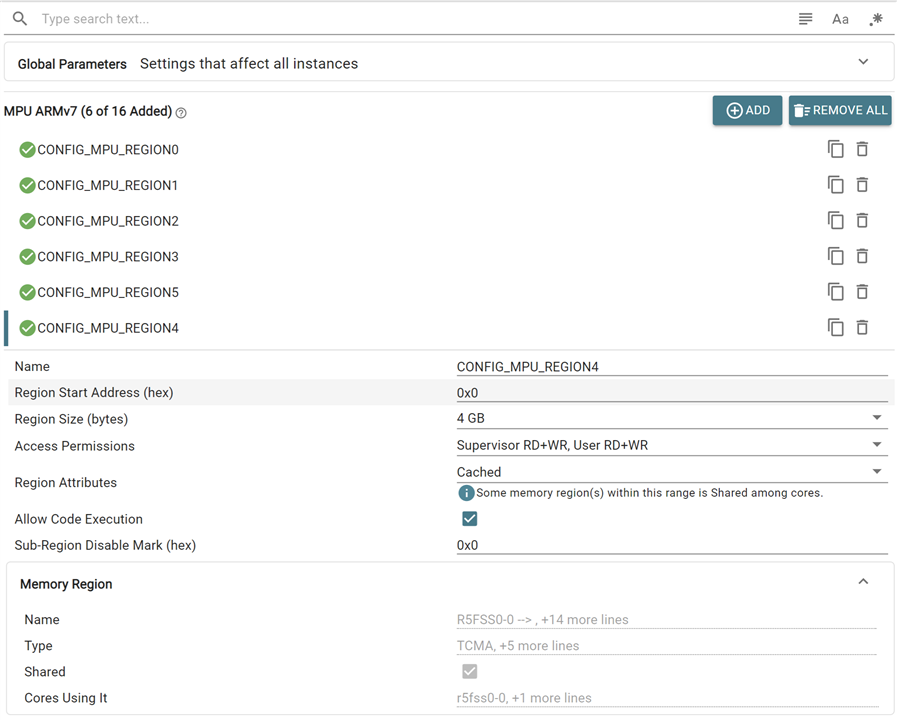

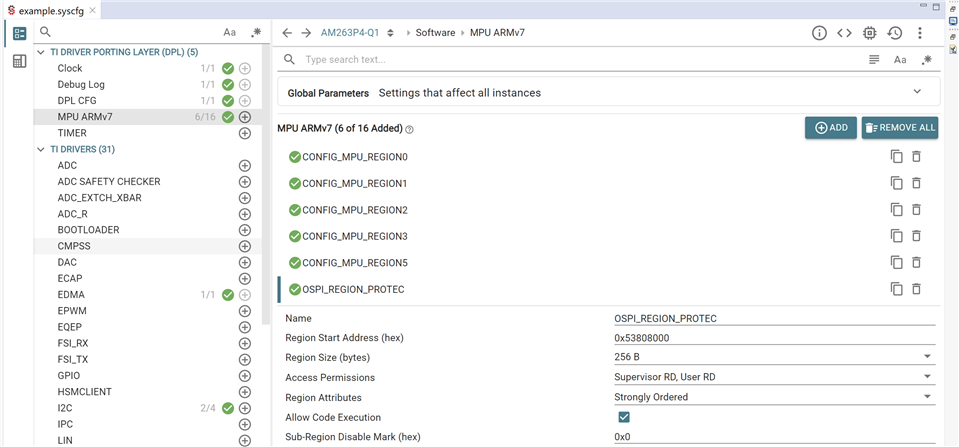

- 当他们为每个 MPU 防火墙配置区域编号0时、会出现一个无法启用的 MPU 防火墙。 (L2OCRAM BANK0 SLV)是否无法配置区域编号0? 如果有区域不可配置、您能否列出哪些区域不可配置?

- 请告诉我 "表5-4981中所列的"AID15 0"的含义。 Programmable_4_MPPA 寄存器字段说明? 另外、请告诉我 Priv ID "ICSSM"、"CPSW"、"外部 ID"以及权限"仿真"和"非安全访问"的含义

此致、

Mari Tunnoda