主题:SysConfig 中讨论的其他器件

工具/软件:

您好:

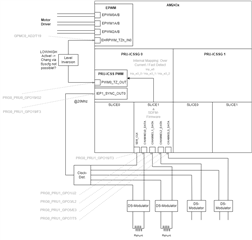

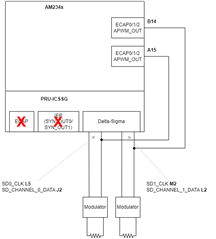

我的问题与位于 PRU-ICSSG 中的 Δ-Σ 滤波器调制器的时钟生成有关。 通常、正如我在 TI 提供的示例中看到的、此任务使用内部 ECAP APWM_OUT 或 IEP SYN_OUT0/1、并且 SD8_CLK 用作公共时钟输入。 但是、由于在硬件上我 CANNOUT 使用内部 ECAP 或 IEP 生成时钟、因此我计划使用"通用"ECAP 模块、如下图所示:

(SDFM 固件应在 ICSSG0的 PRU1内核中运行)

我的主要问题是、这是否可行? 如果可能、我的下一个问题是必须在 SysConfig 中配置什么-"SDFM 时钟配置"需要"ChannelX SDFM 时钟(Hz)"的值会让我感到麻烦-为什么由于 CLK 是在外部提供、因此必须定义一个值?

谢谢、

基督教