主题中讨论的其他器件:SYSCONFIG、LP-AM263、 UNIFLASH

工具/软件:

大家好:

我目前正在使用 LP-AM2612 调试该 ospi_flash_dma 示例并遇到需要您专业知识的问题。 以下是详细信息:

-

原始 JSON 问题

-

使用

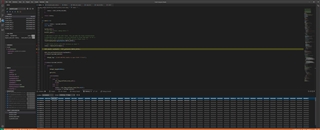

ospi_flash_diag诊断示例生成了一个器件配置 JSON。 -

已尝试将 JSON 导入 CCS v20 、但导入进程无限期挂起(连续"旋转")。

-

-

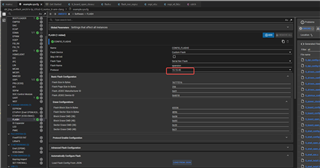

手动配置尝试

-

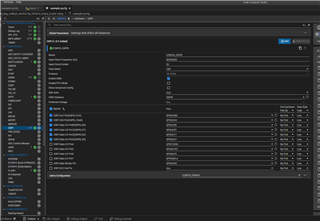

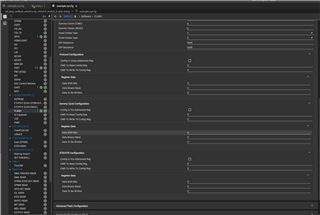

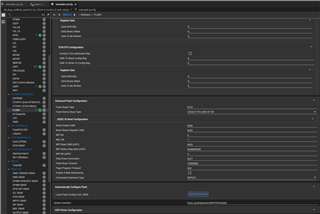

继续根据 JSON 内容手动配置 OSPI 闪存参数。

-

不过、在调试期间、 无信号活动 在 OSPI 接口上观察(通过逻辑分析仪确认)。

-

请求:

请您:

-

验证

ospi_flash_diagJSON 生成/导入流程是否与 CCS v20兼容?

- 在 syscfg 上为 LP-AM2612提供经过验证的 OSPI 闪存配置?

此致

ZX