请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:MSPM0G3507 工具/软件:

您好:

使用 MSPM0G3507进行开发、

它们对 TIMx 事件延迟时间存有疑问。

问题1.

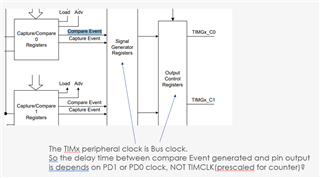

如果 PWM 输出使用"输出控制寄存器"、则比较事件和引脚输出(高电平->低电平)之间的延迟时间取决于哪个(TIMCLK 或外设总线时钟)时钟?

在其测试中、延迟时间与 TIMCLK 相关。 (如果 TIMCLK 使用更快速的时钟(更改预分频值)、则延迟时间更少。)

问题2.

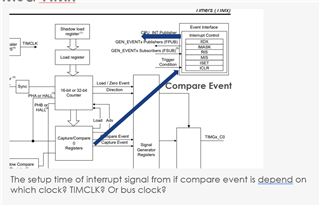

如果 GPIO 输出使用比较中断、则比较事件和引脚输出之间的延迟时间取决于外设总线(PD0或 PD1)和 CPUCLK?

我认为、即使更改 TIMCLK 预分频器、这个延迟时间也是很长的。 这是正确的吗?

谢谢、

GR