工具/软件:

您好:

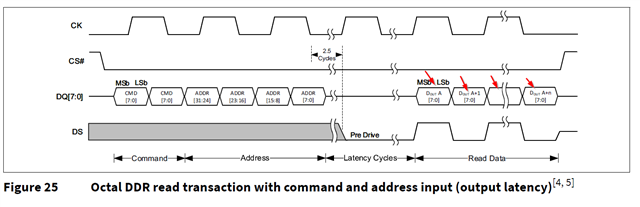

以该 OSPI 闪存为例。 在读取时序图中、命令、地址、虚拟周期之后有几个序列数据周期。 这样可以以突发方式自动读入多个数据。

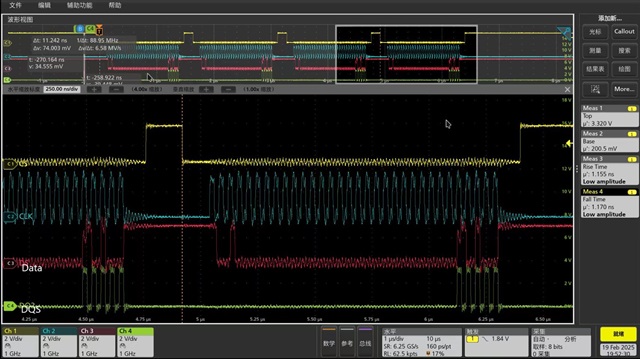

也在电路板上捕获了类似的波形。

但似乎软件不使用突发读取。

在软件中读取10字节数据时、OSPI 输出10 CS、每个 CS 周期都有命令、地址、虚拟周期和5个 DQS 周期。

如果读取8字节数据、则输出8个 CS 周期。

深入研究代码、软件使用 memcpy 进行读取、OSPI 应已经处于存储器映射模式。

根据波形可以看出、有5个 DQS 信号、闪存已经在一个 CS 周期内输出10字节的数据、但软件不知道、仍逐字节读取。

由于存在这种时序行为、吞吐量非常差、浪费了过多的周期、甚至低于单线 SPI、因为它不需要虚拟周期。

#1。 如何利用序列读取来提高吞吐量? 只能使用 DMA 来利用连续突发读取?

#2. 5个 DQS 是否可配置? 我们看到无论要读取多少个字节、它始终是5个序列脉冲。