工具/软件:

尊敬的 TI 团队:

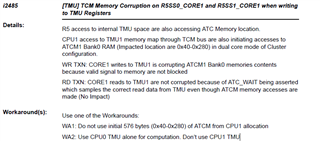

在查看勘误表 i2485 时(“[tmu] R5SS0_CORE1 和 R5SS1_CORE1 上的 TCM 存储器损坏...“) 在最新的 AM263P4 文档中、我发现几个关键方面的说明不清楚。 我想要求澄清以下几点:

-

锁步模式的适用性:

此勘误表引用“R5SS0_CORE1 和 R5SS1_CORE1“来访问 TMU 寄存器、通过 TCM 接口使用 TMU 时、ATCM1 组 0 存储器中会发生损坏。 但是、这些_CORE1 实例仅在相应的 R5SS 配置为拆分模式时存在。 该文本未指定当子系统处于锁步模式(即当_CORE1 为影子_CORE0 时)时、此问题是否也适用。

请确认:

-

此问题是否仅在_Core1 独立执行代码时的拆分模式下才存在?

-

或者、由于 CORE0 发起的 Core1 镜像写入、是否也会在锁步模式下发生损坏?

这很重要、因为在锁步模式下、根据 TMU 集成、Core1 的存储器接口活动仍然可能会影响总线仲裁或写入使能。

-

-

术语不一致–“CPU0"与“与核心名称:

解决方法 WA2 说“单独使用 CPU0 TMU…“、而错误正文明确引用

R5SSx_CORE1。 术语“CPU0"在“在 AM263P4 的上下文中有歧义、并未在 TRM 中明确定义此类命名。R5SS0_CORE0R5SS1_CORE0在拆分模式下、“CPU0"是否“是否指(也可能指)?澄清:

-

WA2 是否意味着只应将每个 R5SS 集群的_CORE0 用于 TMU 访问?

-

或者、它是否仅指 R5SS0_CORE0、这意味着 TMU 的使用应完全限制于特定的集群(例如 R5FSS0)?

-

我们正在评估是在拆分模式下使用两个内核的 TMU 还是将每个集群的使用限制为一个内核–此勘误表具有重大影响。

提前感谢您的支持和澄清。

此致、

Jiri