工具/软件:

大家好!

电源关闭时、当主电源降至 14V 以下时、

我想通过复位 IC 将 nRST 引脚驱动至低电平

并将 IO 引脚设置为高阻抗。

请确认重置行为以确保正确无误。

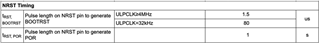

●如果 nRST 引脚由复位 IC 驱动为低电平、

IO 引脚在 1.5us 后是否会变为高阻抗?

※ULPCLK≥4MHz

*1,*2

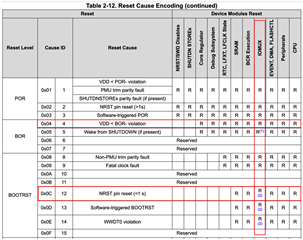

●μ s 当 VDD 下降且 BOR 复位被触发时、

IO 引脚是否会变为高阻抗状态?

*2、*3

在*2 中、指出这些引脚在 BOOTRST 之后变为高阻抗、

但在*3 中、IOMUX 列的 BOR 标记为‘R'、因此我认为 IOMUX 也可通过 BOR 复位并变为高阻抗。

*1 第 33 页,第 7.8 节定时特性

*2 第 1005 页,10.1.1 IO 类型和模拟共享

*3 表 2-12. 复位原因编码(续)

此致、

ITO