Other Parts Discussed in Thread: AM2634, DP83826I

器件型号: AM2634

主题中讨论的其他器件: DP83826I

尊敬的专家:

我的客户尝试使用 DP83826I、在 AM2634 上具有 CPSW3G RMII 接口。 在测试期间、我们发现 R17 端口上的 50MHz RMII1_REF_CLK 缺失。 我们检查由 syscfg (API) 生成的 ti_board_config.c

int32_t EnetBoard_setupPorts (Enet Board_Eth)*ethPorts、

uint32_t numEthPorts)

{

CSL_MSS_CtrlRegs * mssCtrlRegs =(CSL_MSS_CtrlRegs *) CSL_MSS_CTRL_U_BASE;

DebugP_ASSERT (numEthPorts == 1);

EnetBoard_enableExternalMux ();

交换机 (ethPorts->macPort)

{

ENET_MAC_PORT_1 的用例:

CSL_FINS (mssCtrlRegs->CPSW_CONTROL、MSS_CTRL_CPSW_CONTROL_PORT1_MODE_SEL、MSS_CPSW_CONTROL_PORT_MODE_RMII);

休息;

ENET_MAC_PORT_2 用例:

CSL_FINS (mssCtrlRegs->CPSW_CONTROL、MSS_CPSW_CONTROL_PORT2_MODE_SEL、MSS_CPSW_CONTROL_PORT_MODE_RMII);

休息;

默认值:

DebugP_ASSERT (FALSE);

}

/*没有其他事情要做*/

返回 ENET_Sok;

}

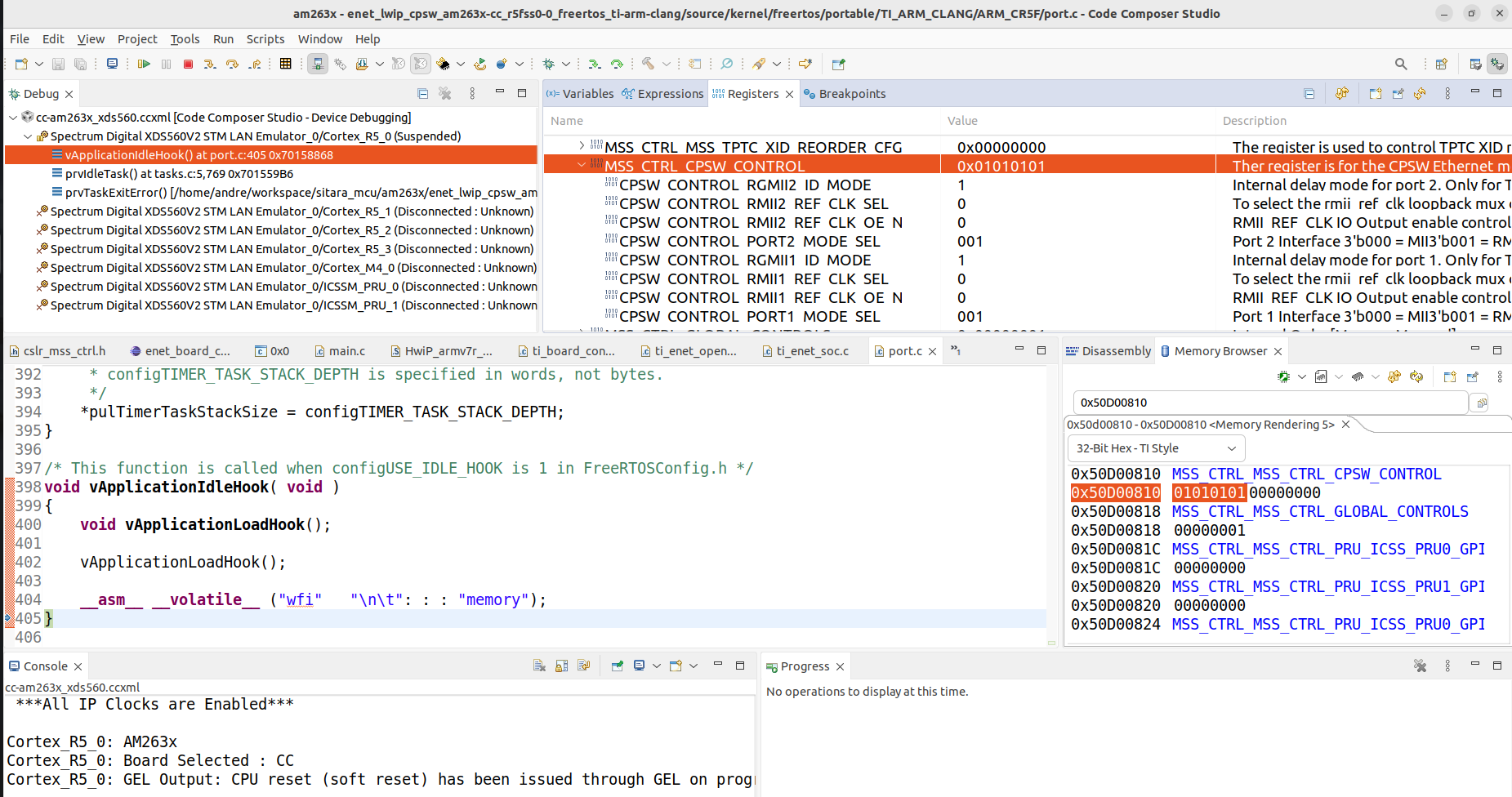

OAD 编程并验证寄存器 MSS_CTRL_CPSW_CONTROL = 0x01010101。 在所有测试期间调用该 API 后、此值不会更改。

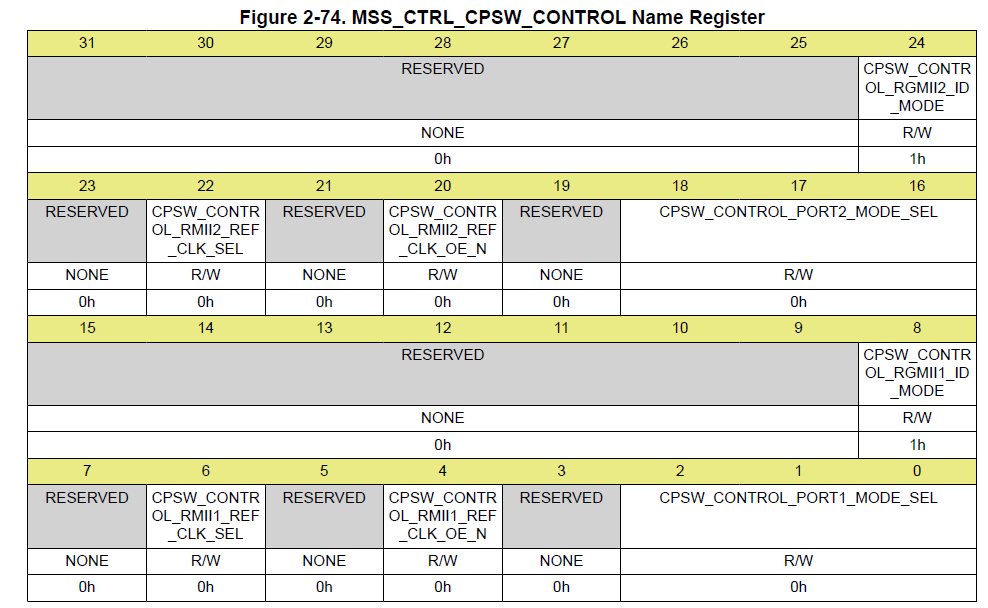

根据 TRM、我们应该能够为 RMII1/RMII2 生成 50MHz 基准时钟。

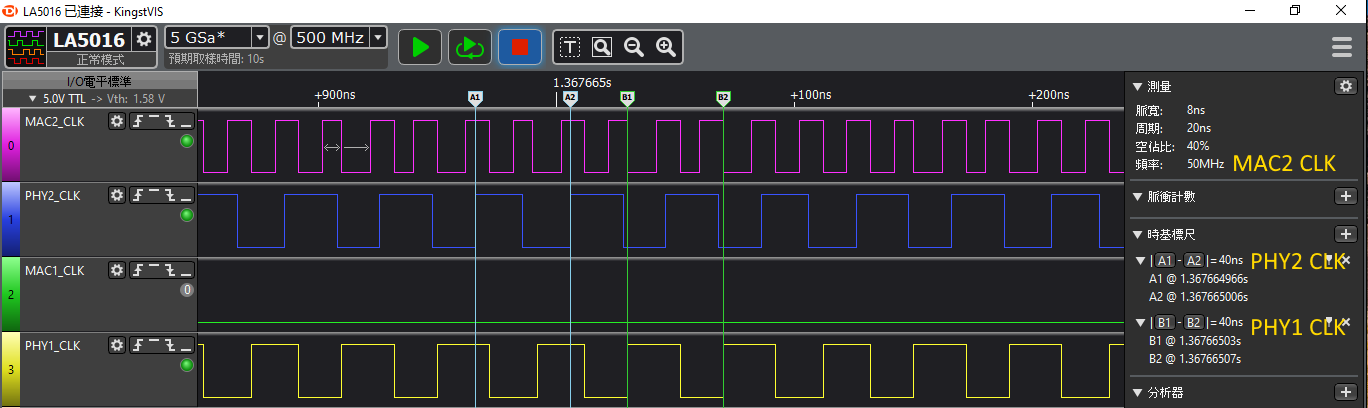

但是、在测量信号时、R17 引脚上的 RMII1_REF_CLK 缺失。

我们还将 R17 设置为 GPIO 并进行切换、我们可以确保 R17 具有正确的连接。 无布局问题。

因此、我们想知道为什么无法生成 RMII1_REF_CLK?

此致

Andre