请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:TM4C1237H6PM 线程中讨论的其他部件:SN75468,

您好,

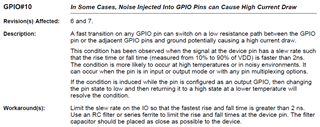

我们使用 TM4C1237H6PM 的 GPIO 点 PF0至 PF4来驱动复合晶体管阵列(TI SN75468)。 在 ESD 测试期间,我们发现放电似乎与达林顿的端口引脚相耦合,并在某种程度上改变了引脚的配置或功能。 放电前,它们工作正常。 放电后,接通的引脚功能关闭,或者可能是三个表示。 它们通常会被轻微的电流泄漏锁定。 重新声明“开”无助于事。 断言“关闭”,然后再次断言“打开”,将 GPIO 引脚恢复为正常功能。 此外,将 GPIO 引脚短路到地电位也会使其恢复正常功能。 当其中一个 GPIO 引脚处于此状态时,我们的供电电流似乎也会增加到最高。

在复合晶体管和 GPIO 引脚之间放置电阻似乎可以解决问题,将每个端口引脚的电容放置到接地也是如此,但似乎需要>0.1uF。 我们目前的假设是,ESD 放电似乎与接地并通过达林顿的保护二极管返回。 向设备耦合附近的接地导线或平面放电,如果没有这些缓解措施之一,则会导致问题。

一些问题:

- GPIO 引脚上的电压干扰是否会使 GPIO 引脚的配置或功能混乱,这可能是沿 FET 锁定事件的一条线发生的情况? 如果是,您是否知道根本原因以及如何缓解这一问题?

- 如上所述,关闭然后再次打开 GPIO 似乎可以解决该问题。 您是否对原因有任何想法,以及可能需要多久才能关闭?

- 我没有在手册中找到有关 GPIO 引脚如何响应从引流中获取的电流的尝试的讨论(我可能错过了),而这些引脚的配置是为 即通过电阻器连接到电容器的 GPIO,该电阻器不会将其最大电流限制为2,4或8mA 的配置。 如果 GPIO 设为2 mA,但名义上会为10 mA 持续一毫秒或更长,是否会出现问题?

- 您是否可以共享 GPIO 的输出电路,以便我们可以查看可能发生的情况?

谢谢,

迈克