“线程:测试”中讨论的其它部件

您好,在测试 SRAM 2位 ECC 故障注入时,在正常情况下,应触发 ESM3.3和 ESM3.5的中断。 但是,根据调试和打印信息,ESM3.7的闪存也导致了不可纠正的错误,但我没有导致闪存故障。 这是什么原因? 这是正常的吗? 非常感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,在测试 SRAM 2位 ECC 故障注入时,在正常情况下,应触发 ESM3.3和 ESM3.5的中断。 但是,根据调试和打印信息,ESM3.7的闪存也导致了不可纠正的错误,但我没有导致闪存故障。 这是什么原因? 这是正常的吗? 非常感谢。

您是否意味 着未设置 FEDACSTATUS 的位8? 如果出现2位 ECC 错误,则应设置此位。

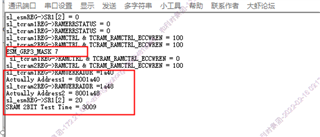

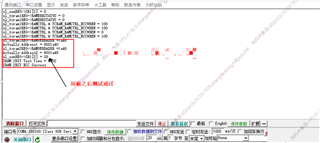

另一个问题是,执行 SRAM_ECC_ERROR_ENCED_2BIT 测试时,测试结果失败,调试信息被打印。 如果发现 SR1[2]的位3未设置,但输入了数据中止中断,但此标志为“未设置。”

SR1[2]通常应为0x28,但打印结果为0x20,测试函数的返回结果也是失败。我不理解两者之间的影响。

请回复,非常感谢。

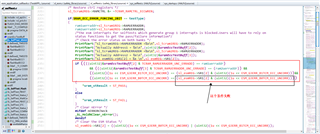

后来,我阻止异常响应状态语句闪烁,我发现测试可以通过。 原因是什么? 测试是否由于 SRAM 2BIT 测试期间生成异常闪存中断而失败?

您好,晓红,

~引用 userid="465499" url="支持/微控制器/基于 ARM 的微控制器-组/基于 ARM 的微控制器/f/基于 ARM 的微控制器- forum/1077218/tms570ls3137-questions -about-sram2-bit-ecc- fault-injection -用于强制执行 tms3137/3988IT_spm_explin_ps_cpr_cpr_cpr_cpr_cprash_cprash[2]570IT_cprash_cpr_cpr_cpr_cpr_cpr_cprash_cprash_cprash_cpr_FEDACSTATUS 位不应设置为 SRAM ECC 错误,而应设置为闪存 ECC 错误。

我在上一篇帖子中的消息是:“如果出现2位闪存 ECC 错误,应该设置此位。”

由于设置了 ESM3.7,因此“else if((ESM_Grp3_mask ==(((grp_channel&ESM_Grp3_mask ))”和(ESM_G3ERR_FMC_Uncorr ==(grp_channel&0x0000ffff))”将变为 true。 您能否检查 ESM3.7的设置时间,SRAM 自检前或 SRAM 自检期间?

SR[2]的位3和位5是由偶数地址和奇数地址上的2位 ECC 错误引起的。

偶数地址为:0x08000000 + N*0x08 ,其中 N=0,2,4,6,8,...

ODD 地址是:0x08000000 + N*0x08 ,其中 N=1,3,5,7,...